FPGA 是什么

FPGA(Field Programmable Gate Array),现场可编程门阵列,一种半定制的数字集成电路。FPGA 凭借其灵活性高、开发周期短、处理性能强(并行)等特点,广泛应用于通信、图像处理、医疗等领域。随着科技的进步,FPGA 在人工智能、5G 和自动驾驶等领域也有一席之地。

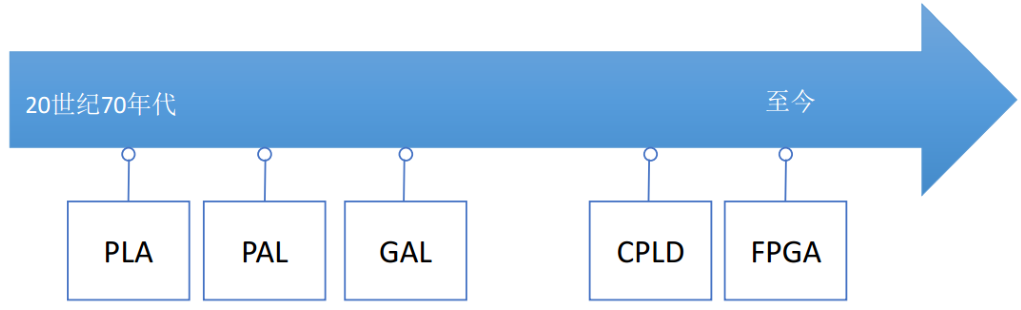

FPGA 它是在 PAL、GAL、CPLD 等可编程器件的基础上进一步发展的产物。它是 作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路个数有限的缺点。

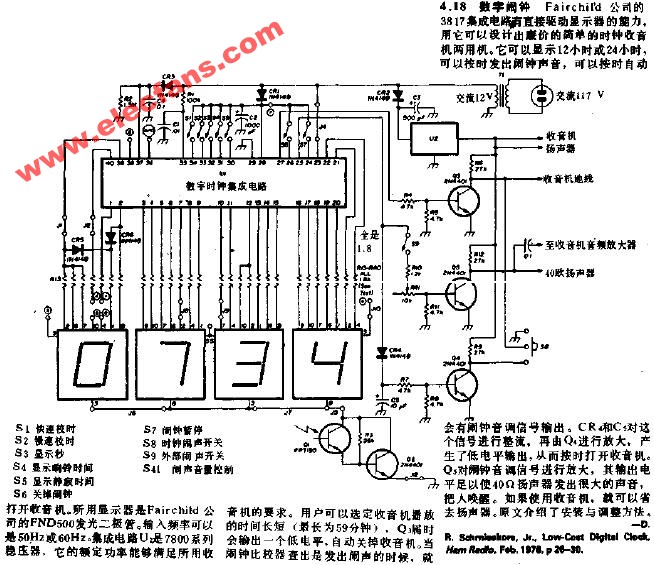

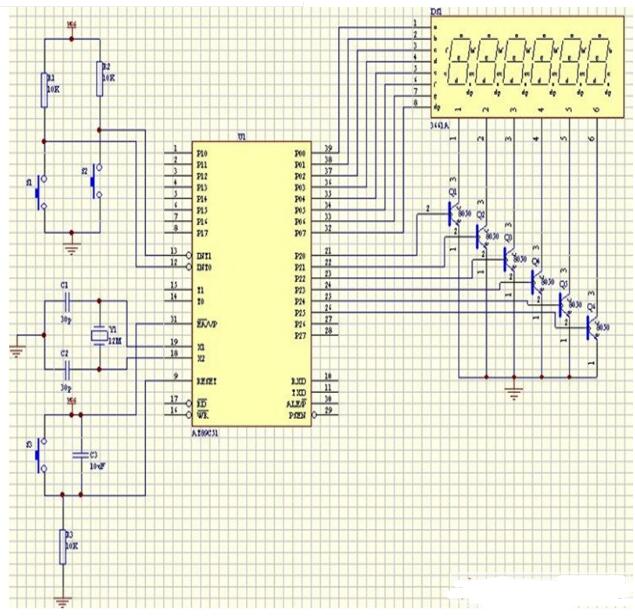

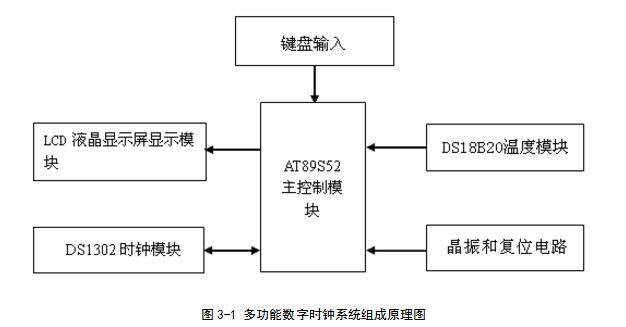

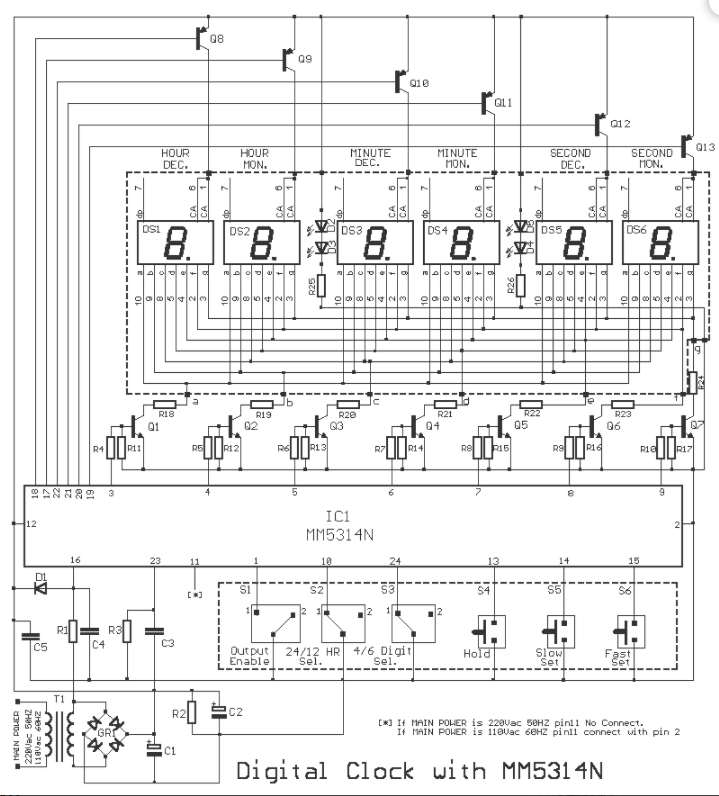

比如用面包板搭建数字时钟电路;虽然电路是一个数字时钟,里面有晶振、蜂鸣器、数码管,以及各种 74 系列的小芯片,这些小芯片能够实现的功能也就相当于几个逻辑门,如果你亲自动手去搭建它,肯定会知道搭建该电路是非常麻烦的,一根线一根线去连接,不断对照原理图,生怕搭错一根线,搞不好心态就崩了。

这仅仅是搭建一个简单的数字时钟就这么多跟线了。如果我们想要实现更加复杂的功能,那么我们就要犯难了,因为我们需要使用几十个或者上百个这种专用小芯片来完成,这样就会使得电路板的布局、布线变得困难,还会极大的影响到整个系统的性能,而且搭出来的电路体积庞大,也不美观,实用性极差,所以这种方式毫无疑问是不行的。

为了改变这种情况,大家就想到了一个办法,那就是通过专用集成电路(ASIC)来实现,我们可以将要实现的特定需求交给 ASIC 厂商,让他们设计出一个专用集成电路芯片,这样就可以解决这种问题了。

比如说,我们把数字时钟功能要求交给 ASIC 厂商,ASIC 厂商就会根据数字时钟功能要求设计出一个专用集成电路芯片,这一个小小的芯片它其实就完成了我们数字时钟电路功能。这种方法虽然很好,但同时也会带来很多其他的问题,比如说,生成周期长,芯片难验证,芯片内部电路不可以更改等等问题。于是人们就开始不断地去探索,看看有没有什么办法既能让我很好的实现功能,又能解决定制电路的不足。

于是 FPGA 应运而生,于 1985 年由 Xilinx 创始人之一 Ross Freeman 发明,属于可编程逻辑器件 PLD(Programmable Logic Device)的一种。

Xilinx A7 系列 FPGA 芯片

真正意义上的第一颗 FPGA 芯片 XC2064 为 Xilinx 所发明,这个时间差不多比著名的摩尔定律晚 20 年左右,但是 FPGA 一经问世,后续的发展速度之快,超出大多数人的想象。

我们要知道一块专用的 ASIC 定制集成电路的芯片他在出厂前功能就已经定死了,就拿上面的数字时钟来举例,假如我现在拿到一块全新的数字时钟芯片,那么我只需要看看厂家给我提供的数据手册,看看它是怎么操作的,可能仅仅只需要给它通上电然后简单的配置一下它就能工作了。

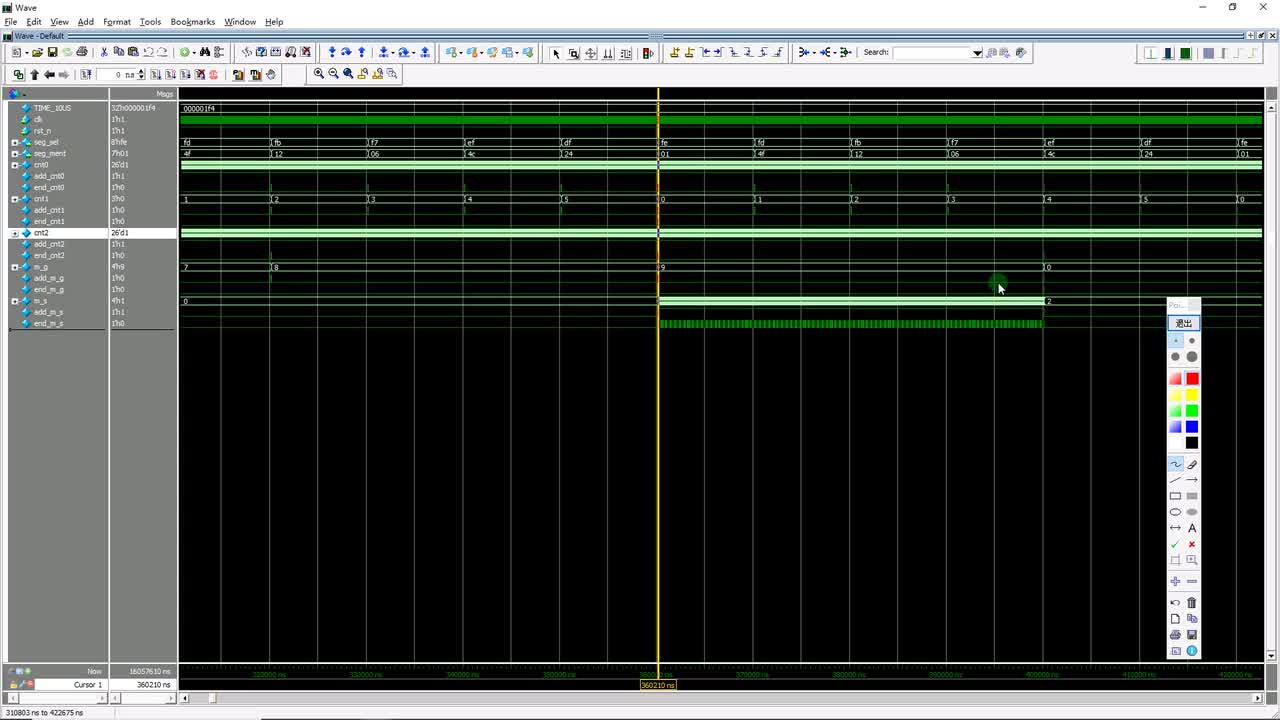

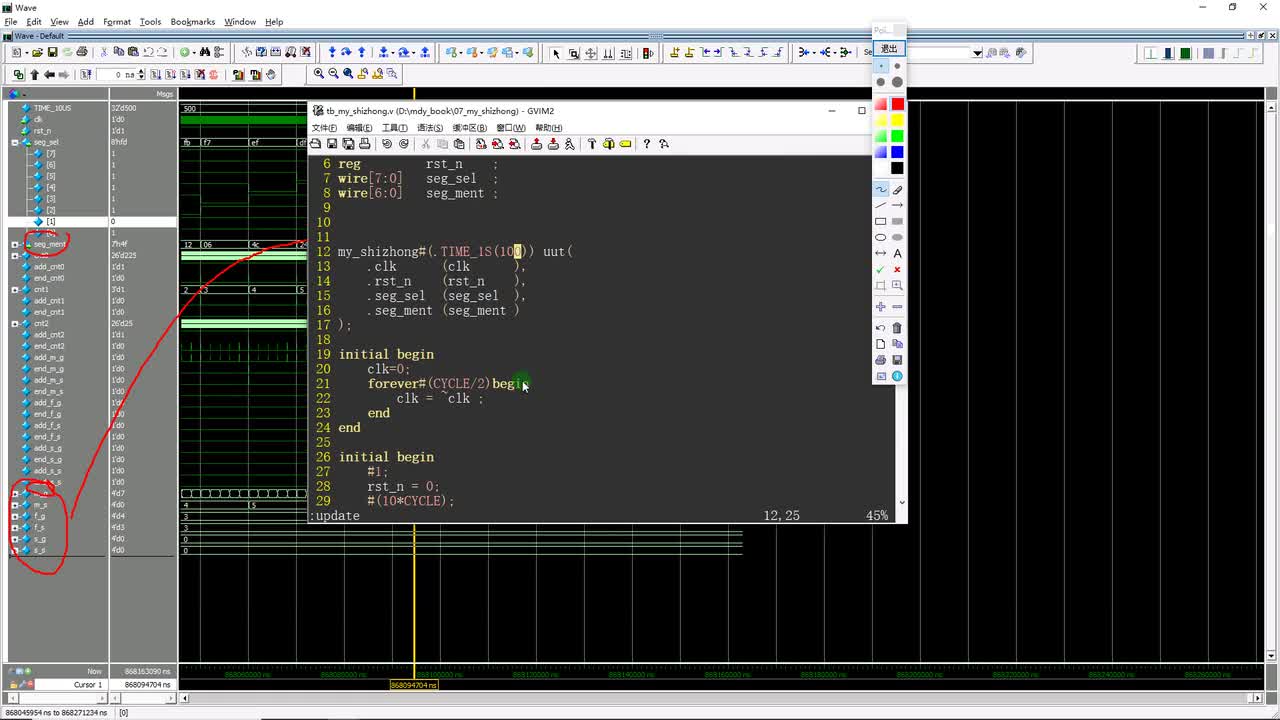

它的功能是不可更改的,就只能跑个数字时钟,而且它内部电路是啥样的我也不知道,虽然用起来简单,但是缺乏灵活性,但 FPGA 就不一样了,它在出厂的那一刻是不具备任何功能的,可以说就是一张白纸。你可以在这张白纸上肆意创作,你想要它实现数字时钟的功能没问题,通过特定的编辑语言,例如 Verilog、VHDL 等硬件描述语言将数字时钟的逻辑编写好,下载到 FPGA 内部,它就会生成一个数字时钟的电路,去完成数字时钟的功能。当你不想要这个功能了,没问题你可以随时将内部程序擦除,或者用一个新的设计去覆盖原有的设计。理论上我们可以用 FPGA 去生成一个任意我们想要的功能,正是基于这种强大的可编辑能力,FPGA 近年来越来越受到市场的认可,在未来 FPGA 的适用范围必将越来越广阔。

FPGA 有什么用

FPGA 所能应用的领域大概可以分成六大类:

1)通信领域

FPGA 在通信领域的应用可以说是无所不能,得益于 FPGA 内部结构的特点,它可以很容易地实现分布式的算法结构,这一点对于实现无线通信中的高速数字信号处理十分有利。因为在无线通信系统中,许多功能模块通常都需要大量的滤波运算,而这些滤波函数往往需要大量的乘和累加操作。而通过 FPGA 来实现分布式的算术结构,就可以有效地实现这些乘和累加操作。尤其是 Xilinx 公司的 FPGA内部集成了大量的适合通信领域的一些资源比如:基带处理(通道卡)、接口和连接功能以及 RF(射频卡)三大类:

(1)基带处理资源

基带处理主要包括信道编解码(LDPC、Turbo、卷积码以及 RS 码的编解码算法)和同步算法的实现(WCDMA 系统小区搜索等)。

(2)接口和连接资源

接口和连接功能主要包括无线基站对外的高速通信接口(PCI Express、以太网 MAC、高速 AD/DA 接口)以及内部相应的背板协议(OBSAI、CPRI、EMIF、LinkPort)的实现。

(3)RF 应用资源

RF 应用主要包括调制/解调、上/下变频(WiMAX、WCDMA、TD-SCDMA 以及 CDMA2000 系统的单通道、多通道 DDC/DUC)、削峰(PC-CFR)以及预失真(Predistortion)等关键技术的实现。

总而言之只要你 FPGA 学的好,在通信领域你绝对可以大展身手。

2)数字信号处理领域

在数字信号处理领域 FPGA 同样所向披靡,主要是因为它的高速并行处理能力。FPGA 最大优势是其并行处理机制,即利用并行架构实现数字信号处理的功能。这一并行机制使得 FPGA 特别适合于完成 FIR 等数字滤波这样重复性的数字信号处理任务,对于高速并行的数字信号处理任务来说,FPGA 性能远远超过通用 DSP 处理器的串行执行架构,还有就是它接口的电压和驱动能力都是可编程配置的不像传统的 DSP 需要受指令集控制,因为指令集的时钟周期的限制,不能处理太高速的信号,对于速率级为 Gbps 的 LVDS 之类信号就难以涉及。所以在数字信号处理领域 FPGA 的应用也是十分广泛的。

3)视频图像处理领域

随着时代的变换,人们对图像的稳定性、清晰度、亮度和颜色的追求越来越高, 像以前的标清(SD)慢慢演变成高清(HD),到现在人们更是追求蓝光品质的图像。这使得处理芯片需要实时处理的数据量越来越大,并且图像的压缩算法也是越来越复杂,使得单纯的使用 ASSP 或者 DSP 已经满足不了如此大的数据处理量了。这时 FPGA 的优势就凸显出来了,它可以更加高效的处理数据,所以在图像处理领域在综合考虑成本后,FPGA 也越来越受到市场的欢迎。

4)高速接口设计领域

其实看了 FPGA 在通信领域和数字信号处理领域的表现,我想大家也已应该猜 到了在高速接口设计领域,FPGA 必然也是有一席之地的。它的高速处理能力和多达成百上千个的 IO 决定了它在高速接口设计领域的独特优势。

比如说我需要和 PC 端做数据交互,将采集到的数据送给 PC 机处理,或者将处理后的结果传给 PC 机进行显示。PC 机与外部系统通信的接口比较丰富,如 ISA、PCI、PCI Express、PS/2、USB 等。传统的做法是对应的接口使用对应的接口芯片,例如 PCI 接口芯片,当我需要很多接口时我就需要多个这样的接口芯片,这无疑会使我们的硬件外设变得复杂,体积变得庞大,会很不方便,但是如果使用 FPGA 优势立马就出来了,因为不同的接口逻辑都可以在 FPGA 内部去实现,完全没必要那么多的接口芯片,在配合 DDR 存储器的使用,将使我们接口数据的处理变得更加得心应手。

5)人工智能领域

如果大家比较喜欢关注科技板块的新闻的话最近一定会被 5G 通信和人工智能充斥 眼球,确实 21 世纪已经不知不觉走到了 2020 年,在这 20 年间,人工智能迅速发展,5G 的顺利研发也使人工智能如虎添翼,可以预见,未来必将是人工智能的天下。

FPGA 在人工智能系统的前端部分也是得到了广泛的应用,例如自动驾驶,需要对行驶路线、红绿灯、路障和行驶速度等各种交通信号进行采集,需要用到多种传感器,对这些传感器进行综合驱动和融合处理就可以使用 FPGA。还有一些智能机器人,需要对图像进行采集和处理,或者对声音信号进行处理都可以使用 FPGA 去完成,所以 FPGA 在人工智能系统的前端信息处理上使用起来得心应手。

6)IC 验证领域

IC 这个词大家可能一听到就觉得特别高深,不是凡人所能触及到的,而 IC 设计更是一些神人才能胜任的工作。不可否认的是 IC 设计门槛确实比较高,但是我们也没必要把它过于神话,其实简单点来讲我们可以拿 PCB 设计来与之比较,PCB 是拿一个个元器件在印制线路板上去搭建一个特定功能的电路组合,而 IC 设计呢是拿一个个 MOS 管,PN 节在硅基衬底上去搭建一个特定功能的电路组合,一个 宏观一个微观。PCB 如果设计废了大不了重新设计再打样也不会造成太大损失,但是如果 IC 设计废了再重新设计那损失就很惨重了,俗话说大炮一开,黄金万两,那么在 IC 领域***一开黄金万两也不是吹的,光刻胶贵的要命,光刻板开模也不便宜,加上其他多达几百上千道工序,其中人力、物力、机器损耗、机器保养,绝对是让人肉疼的损失,所以 IC 设计都要强调一版成功。保证 IC 一版成功就要进行充分的仿真测试和 FPGA 验证,仿真验证是在服务器上面跑仿真软件进行测试,类似 ModelSim/VCS 软件;FPGA 验证主要是把 IC 的代码移植到 FPGA 上面,使用 FPGA 综合工具进行综合、布局布线到最终生成 bit 文件,然后下载到 FPGA 验证板上面进行验证,对于复杂的 IC 我们还可以给他拆成几个部分功能去分别验证,每个功能模块放在一个 FPGA 上面,FPGA 生成的电路非常接近真实的 IC 芯片。这样极大的方便我们 IC 设计人员去验证自己的 IC 设计。

FPGA 的生产厂商

两大巨头:Xilinx 和 Altera。

一群小弟:紫光同创、京微雅格、高云半导体、上海安路、西安智多晶等,同国外领先厂商相比,国产 FPGA 厂商不论从产品性能、功耗、功能上都有较大差距。

ZYNQ

ZYNQ = FPGA + ARM 核,可以自己定制电路,同时还可以做普通的嵌入式开发。

Zynq-7000 系列是 Xilinx 公司推出的全可编程片上系统,包含 PS(Processing System,处理器系统)和 PL(Programmable Logic,可编程逻辑)两部分。Zynq SoC 整合了ARM 双核 cortex-A9 处理器和 Xilinx 7 系列 FPGA 架构,使得它不仅拥有 ASIC 在能耗、性能和兼容性方面的优势,而且具有 FPGA 硬件可编程性的优点。

PYNQ:Python Productivity for Zynq = Python + ZYNQ,是 Xilinx 推出的一种开放源代码框架,使用 Python 语言和库,使设计人员可以利用 zynq 中可编程逻辑和微处理器的优势来快速构建高性能的嵌入式应用程序。

补充

PLD:Programmable Logic Device,可编程逻辑器件。

SoC:System on Chip,片上系统。

审核编辑:黄飞

德赢Vwin官网

App

德赢Vwin官网

App

评论