利用FPGA实现双口RAM的设计及应用

概述:为了在高速采集时不丢失数据,在数据采集系统和

2010-04-16 14:08:36 11323

11323

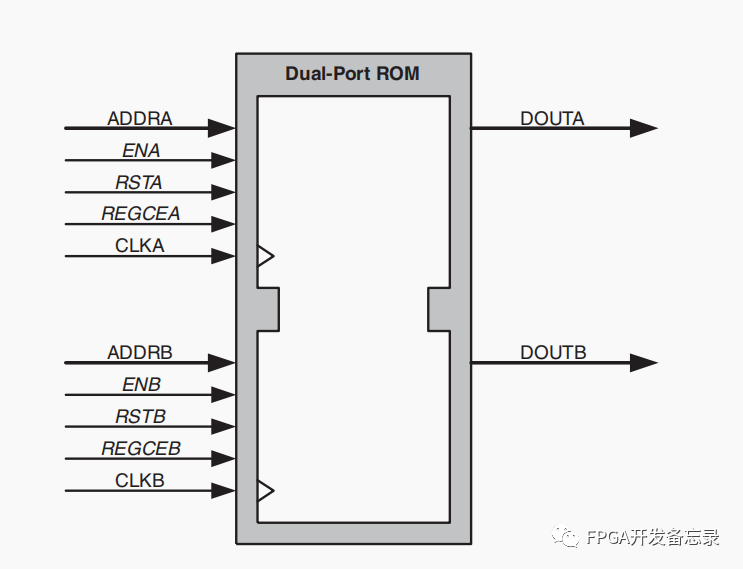

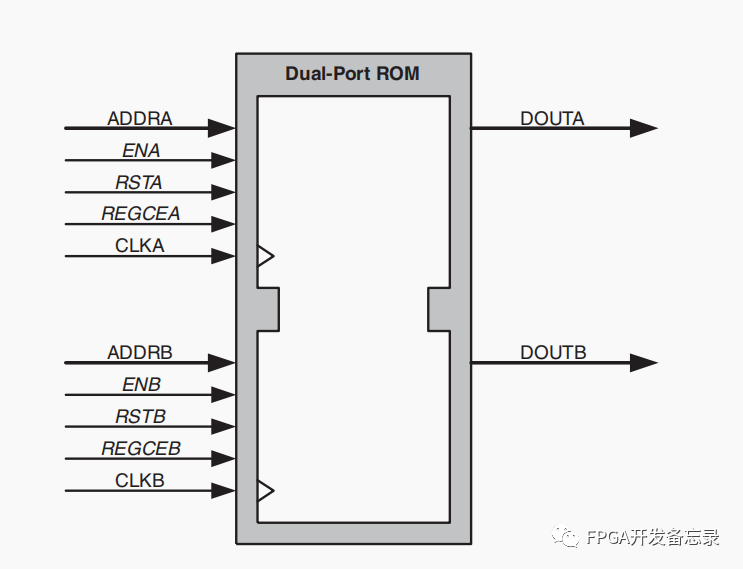

真双口RAM给设计带来很多便利。在高速存储中,需要对连续的数据同时处理,使用简单双口RAM只能读取一个数据,而使用真双口RAM可以同时读取两个数据,这样明显提高读取速度以及处理速度。

2018-06-29 08:54:07 32478

32478

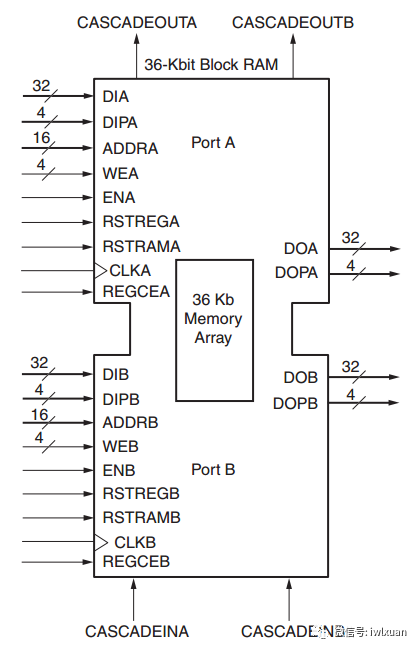

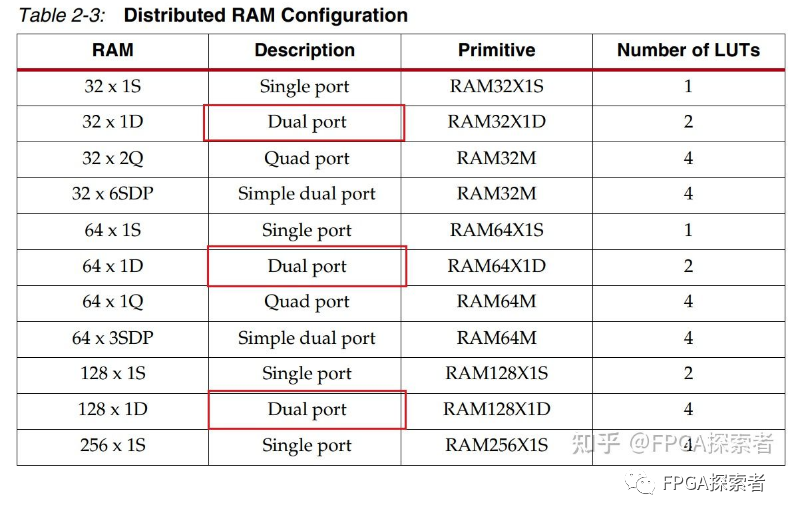

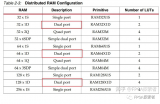

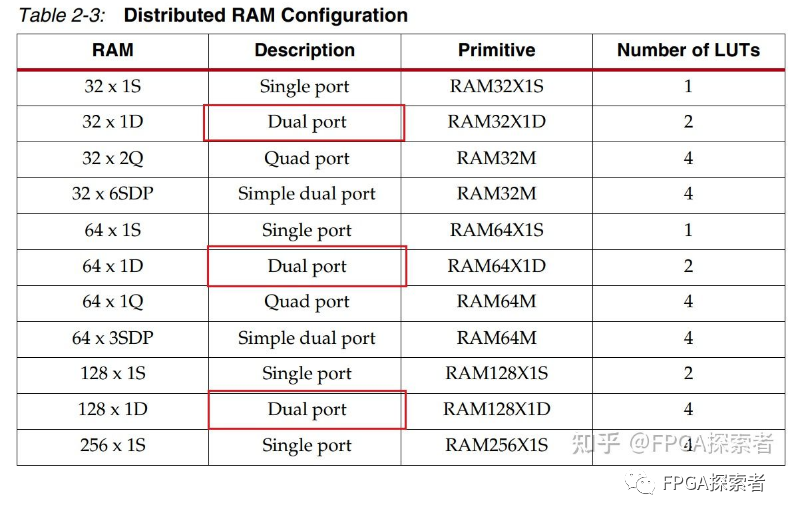

FPGA内嵌的存储器单元包括块RAM(BRAM)和分布式RAM。

2023-08-15 16:11:05 567

567

在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

2023-11-21 15:03:06 548

548

你好,根据Atrix7数据手册ds181,DRAM的最小时钟周期为2.10 ns,因此最大工作频率为479 MHz(参见第22页)。其中,由于切片路由,DRAM的频率将随着其深度的增加而减小。但是,BRAM的最大工作频率表示为509 MHz(参见第24页)。我的问题是,BRAM作为慢组件和基于切片的逻辑作为快速组件,这些值是矛盾的。根据这些值,根据我的理解,BRAM比DRAM更快。如果是,那怎么样?如果没有那么为什么?请尽快回复。[R3] ds181_Artix_7_Data_Sheet.pdf 1963 KB

2020-03-19 09:13:44

大家好。我设计并模拟了简单的RTL with Block RAMin Kintex 7。在合成和实现之后,vivado用于功率估计。当我使用分布式RAM时,会正确报告每个RAM的功耗。但是

2019-03-13 14:21:13

本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有

2023-03-14 17:38:29

;MEM [15] = 8'hf;结束永远@(posedge clk1) if(mem_we)开始 MEM [mem_waddr [3:0]]正如您所看到的,这是简单而传统的分布式RAM描述,具有全宽

2019-06-12 14:17:08

我打算在Virtex7器件中使用分布式RAM作为单端口RAM,用于我的滤波器设计。 RAM将初始配置,然后只有读取将从RAM开始。我的读地址生成来自CLK2,与写时钟CLK1异步。我可以像这样

2019-04-16 09:52:29

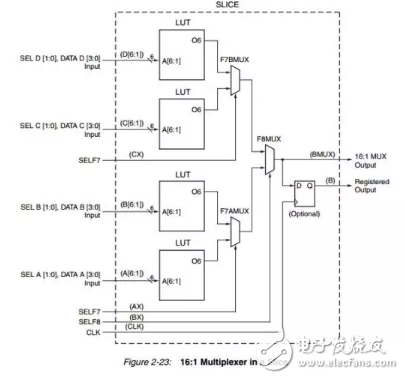

您好!分布式RAM和Block RAM之间究竟有什么区别?两者都只是芯片内存,对吧?但我不知道两者之间的区别。和..下一个问题.. isaboutMUX ..根据7系列概述,7系列FPGA支持全范围

2020-07-19 06:37:51

喜我是这个社区的新手,所以如果这种话题不符合该部分或者我滥用论坛,我会提前道歉。我有一个项目,我需要实例化2000个分布式rams,由2000个数据文件初始化。问题是,当我尝试使用iSim模拟我

2019-03-12 13:01:59

大家好 ...我在实现大小为65535 * 3的分布式RAM时出现问题,在大约2小时内合成时发生了很大的延迟并且没有停止,对这个问题有什么解释吗?提前致谢以上来自于谷歌翻译以下为原文Hello

2019-06-25 11:03:45

几种分布式发电简介2.分布式发电与配电网互联问题3.微型电网技术4.分布式发电(电源)技术应用的障碍和瓶颈5.分布式发电(电源)技术发展方向6.结语

2011-03-11 13:37:39

分布式声波传感系统DAS

2020-12-21 07:48:43

当讨论分布式系统时,我们面临许多以下这些形容词所描述的 同类型: 分布式的、删络的、并行的、并发的和分散的。分布式处理是一个相对较新的领域,所以还没有‘致的定义。与顺序计算相比、并行的、并发的和分布式的计算包括多个PE问的集体协同动作。这些术语在范围一卜相互覆盖,有时也交换使用。

2020-03-31 09:01:18

分布式软件系统分布式软件系统(Distributed Software Systems)是支持分布式处理的软件系统,是在由通信网络互联的多处理机体系结构上执行任务的系统。它包括分布式操作系统

2009-07-22 14:53:12

我今天正在实现FIFO,我想知道FIFOPrimitive和Block RAM实现之间的区别是什么。根据我的理解,它们使用相同的底层RAM原语,但FIFOPrimitive不能有不同的R / W方面

2019-02-27 14:16:45

设计理念HarmonyOS 是面向未来全场景智慧生活方式的分布式操作系统。对消费者而言,HarmonyOS 将生活场景中的各类终端进行能力整合,形成“One Super Device”,以实现

2020-09-22 17:11:07

Quartus II 中定制的RAM是分布式的还是块的

2014-03-10 17:51:45

嗨,为了调试系统,我需要在系统运行时动态读取Block-RAM内容....我只有JTAG线,我不能在FPGA中制作一个特定的块用于读取内容并通过JTAG等发送它们。我可以使用ISMP 13.2作为

2019-06-11 07:36:08

TSP分布式控制有什么优势?TSP分布式控制提高了测试速度并且降低了测试成本。

2021-05-12 06:19:56

Vivado综合可以理解多种多样的RAM编写方式,将其映射到分布式RAM或块RAM中。两种实现方法在向RAM写入数据时都是采取同步方式,区别在于从RAM读取数据时,分布式RAM采用异步方式,块RAM

2020-09-29 09:40:40

`Xilinx FPGA入门连载48:FPGA片内RAM实例之RAM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1新建源文件打开

2016-01-22 13:39:24

《无线通信FPGA设计》分布式FIR的并行改写,结果与matlab仿真结果基本吻合

2017-02-26 09:09:47

之前我们分享过分布式软总线和分布式数据管理,今天主要说一下OpenHarmony的分布式任务调度,分布式任务调度是建立在分布式软总线和分布式数据管理基础之上,目标是为了构建统一的分布式服务管理(发现

2022-07-18 17:06:45

我正在运行Spartan 6 block ram的模拟。时钟速度为100Mhz。块ram的写作运作良好。我可以在内存中看到数据。但是当我读取数据时,输出有2个时钟的延迟。在块ram用户guidt中

2019-07-25 08:15:27

有读取和/或写入数据总线。 写入RAM通常是同步完成的。阅读通常是同步进行的,但有时可以异步进行。 Blockram与分布式RAM现在,FPGA中有两种内部RAM:Blockrams和分布式RAM。通常

2020-09-10 11:11:57

嗨,我在使用BRAM时出现溢出问题(110%)有没有办法使用tcl命令,我说某些单元格,实现它们作为分布式RAM而不是BRAM?修改一些属性或什么?谢谢,以上来自于谷歌翻译以下为原文Hi, I'm

2018-10-31 15:23:19

大家好,我正在尝试用VHDL中的初始值实现分布式RAM。我的目标是Virtex-5- 某处有一个例子吗?我知道有些Virtex组件确实有一个可以使用泛型传递的初始值 - 我应该将它与全局重置或其他

2019-02-26 11:15:14

在我的一个FPGA类中,我被要求使用coregen创建一个blcok ram(8dx16w),单端口ram IP。我在Windows XP,Service Pack 3上使用Xilinx ISE

2019-06-05 13:39:14

您好,我正在Virtex7上实现(127x8)即(深度x宽度)内存。我有以下问题1.使用速度,效率和功率使用的分布式ram或block ram interms来实现它是否可行。2.他们使用分布式

2020-03-23 07:17:45

。块RAM(BRAM),容量较大,数量少,速度较快。分布式RAM:容量小,数量多,速度不如BRAm快。一般使用方法和接口是一样的。

2018-08-23 09:14:59

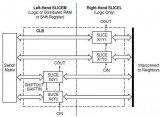

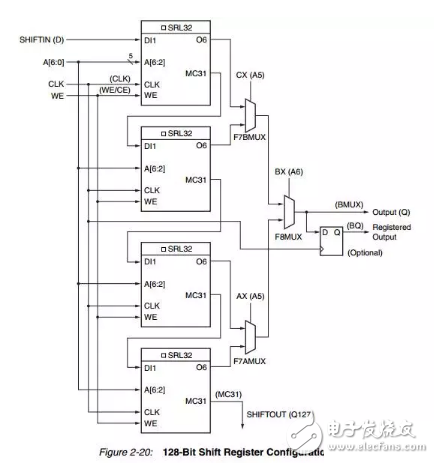

一、查找表LUT就是查找表,对于4输入的LUT而言,实际上就是4位地址位,一位数据位的存储器,能够存储16位数据,所以我们在FPGA设计中可以用LUT组建分布式的RAM。这样也可以解释我们在设计中

2021-07-28 08:42:17

一种基于ZigBee和ModBus的分布式电子警察系统设计

2021-05-31 06:24:15

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。1.实验原理Xilinx

2021-01-07 16:05:28

使用 Jmeter 进行分布式测试;检索日志

2023-05-10 13:00:46

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

的选择无线分布式采集来进行。现有的无线分布式采集系统中,往往使用单片机、DSP等作为系统的主控控制单元。但是由于其自身工作特点,往往对于精确的定时控制以及并行处理能力上比FPGA弱。

2019-10-14 07:10:38

分布式车身控制系统的结构是怎样构成的?分布式车身控制系统有哪些功能?

2021-05-13 07:03:30

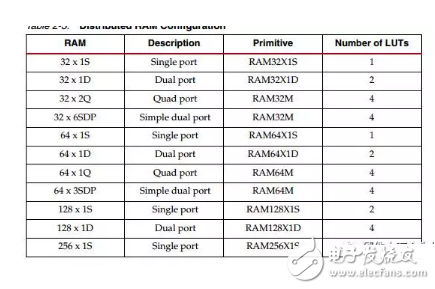

如何在第17和第20页上安装clb用户指南(ug384 v1.1)中描述的RAM32X2Q或RAM64X1Q。这些不会出现在用于hld或原理图输入的spartan库中。他们也没有在软件的13/2版本中显示分布式内存生成器。这是额外的成本项目还是我还缺少另一件事?

2019-10-25 09:34:48

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一个单独的奇偶校验写使能位,但在FPGA RAM中没有单独的Pariaty写使能位。 如何实现ASIC RAM奇偶校验写入启用ino FPGA RAM。谢谢娜文G K.

2020-04-24 09:37:05

什么是分布式天线系统?如何对分布式天线系统(DAS)进行优化?

2021-05-24 06:03:56

什么是分布式干扰系统?分布式干扰系统是一种综合化、一体化、小型化、网络化和智能化系统,是将众多体积小,重量轻,廉价的小功率侦察干扰机装置在易于投放的小型平台上,撒布在接近***扰目标空域地,通过指令

2019-08-08 06:57:44

作者:liuxun,HarmonyOS测试架构师HarmonyOS是新一代的智能终端操作系统,给开发者提供了设备发现、设备连接、跨设备调用等丰富的分布式API。随着越来越多的开发者投入到

2021-12-13 18:07:58

嗨,我正在xilinx virtex7上使用分布式RAM实现((深度)128x(宽度)8)位存储器结构。从理论上讲,它应该占用128x8 = 1024; 1024年至1064年= 16; 16/4

2020-04-06 07:19:30

我正在尝试使用virtex 5上的Block RAM来实现延迟线。延迟线需要将数据延迟一个时钟周期。这可能使用Block RAM吗?我尝试使用简单的双端口RAM,“先读”作为操作模式。我正在写一个

2020-06-18 15:40:33

你好,我正在开发一个在VC709开发板上使用Virtex7 FPGA的系统。该应用程序使用32Mb的板载Block RAM作为设计中的存储元件。 FPGA配置序列完成后,有没有一种方法可以使用PC上的JTAG / USB接口直接写入和读取Block RAM的内容?谢谢,

2019-09-29 14:00:01

分布式的滤波器算法是什么?一种基于FPGA分布式算法的滤波器设计实现

2021-04-29 07:13:23

,维克多Rdp_fifo3.v 3 KB以上来自于谷歌翻译以下为原文I am trying to use the block ram on Xilinx Spartan 3AN (XC3S400AN

2019-06-04 09:08:32

嗨,我想为我的设计使用比特流加密,我遇到了一个关于9K Block RAM的问题,在答案记录39999中描述了r然后我决定在我的设计中删除所有9k Block RAM并将它们更改为16k Block

2019-06-06 07:23:18

嗨!我有一个关于分布式RAM和Block RAM的问题。芯片中有menexternalmemory或内存吗?请详细告诉我。谢谢!

2019-11-07 09:07:16

一个关于分布式RAM时序的问题。你可以看到Attchments。在蓝线中,如果CLK将0更改为1. AI / BI / CI / DI将被复制到输出。在这种情况下,蓝色十字架的意思是什么?我不知道它

2019-11-07 09:31:52

我想知道“逻辑单元”的意思..我知道“Block RAM”,“分布式RAM”“CLB”......以及ETC ..但是,我不知道“Logic Cell”..请让我知道..谢谢!

2019-11-08 16:38:38

为了在高速采集时不丢失数据,在数据采集系统和CPU之间设置一个数据暂存区。介绍双口RAM的存储原理及其在数字系统中的应用。采用FPGA技术构造双口RAM,实现高速信号采集系

2010-02-11 11:20:27 69

69 基于Actel FPGA 的双端口RAM 设计双端口RAM 芯片主要应用于高速率、高可靠性、对实时性要求高的场合,如实现DSP与PCI 总线芯片之间的数据交换接口电路等。但普通双端口RAM 最大

2010-11-15 17:44:19 82

82 RAM,RAM工作原理是什么?

RAM (Random Access Memory随机存贮器)是指通过指令可以随机地、个别地对每个存储单元进行访问、访问所需时间基本固定、且与存

2010-03-24 16:03:02 10297

10297 GD32-Colibri-F207实验板RAM-RAM,很好的GD32资料,快来学习吧。

2016-04-21 10:49:49 2

2 带有异步写/同步读的SRAM,其中的同步读取可以使用与分布式RAM相关联的触发器实现。

2017-02-11 13:54:59 2160

2160

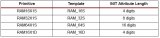

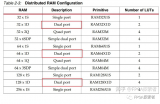

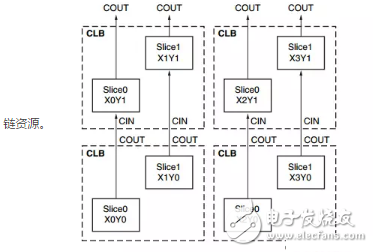

在赛灵思Spartan-3、3E等系列的FPGA中,其逻辑单元CLB中一般含有不同数量的单端口RAM(SRAM)或者双端口RAM(DRAM),这里的“单”或者“双”是由我们开发人员定义的。

2017-02-11 13:56:11 6348

6348

前面简要介绍了Spartan-3系列FPGA中分布式RAM的基本特性。为什么不从更高级的Virtex系列入手呢?我仔细看了一下各个系列的介绍、对比,Spartan系列基本就是Virtex系列的精简版,其基本原理是一样的,所以从简单的入手来融会贯通未尝不是一个好办法。

2017-02-11 13:57:40 1176

1176

前面讲了分布式RAM的方方面面,下面以RAM_16S为例,分别给出其在VHDL和Verilog HDL下面的模板代码(在ISE Project Navigator中选择 Edit---

2017-02-11 13:59:33 1323

1323 FPGA内部的RAM M9K

2017-04-07 11:40:04 4

4 FPGA中RAM的使用探索。以4bitX4为例,数据位宽为4,深度为4。

2018-03-28 17:07:28 9726

9726

大家好,又到了每日学习的时间了,今天我们来聊一聊在FPGA设计中RAM的两种使用方法,RAM是用来在程序运行中存放随机变量的数据空间,使用时可以利用QuartusII的LPM功能实现RAM的定制

2018-06-08 11:30:28 19562

19562 本文介绍了如何在FPGA 中利用Block RAM 的特殊结构实现HDTV视频增强算法中灰度直方图统计。

2019-07-10 08:10:00 2578

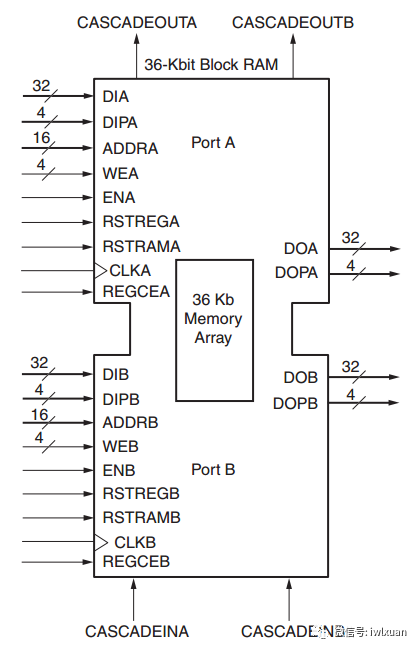

2578 了解新的Block RAM级联功能,如何使用它,以及如何利用其功能和性能优势。

2018-11-23 06:56:00 4470

4470 些大材小用,因此xilinx公司在其FPGA内部专门集成了很多存储器模块,称作Block RAM,其犹如slice海洋当中的一颗颗明珠,专门实现数据暂存功能,且每个时钟区域都布置了若干个Block

2020-11-23 14:08:43 7379

7379

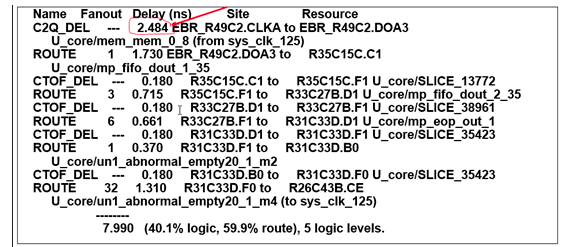

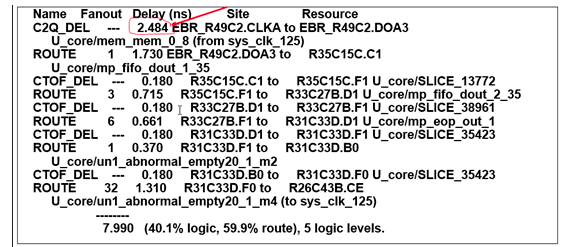

关于Block RAM的寄存器输出,我们在《通过RTL改善时序的技巧之Block RAM的输出》中介绍过。如果我们在时序报告中关键路径上看到这样一条信息: 在第一级的C2Q delay(clock

2021-03-26 15:50:27 1570

1570

本文档的主要内容详细介绍的是FPGA的RAM存储资源详细资料说明包括了:1、 FPGA存储资源简介,2、 不同厂家的 Block RAM 布局,3、 块 RAM 和分布式 RAM 资源,4、 Xilinx Block RAM 架构及应用

2020-12-09 15:31:00 10

10 在FPGA中block ram是很常见的硬核资源,合理的利用这些硬件资源一定程度上可以优化整个设计,节约资源利用率,充分开发FPGA芯片中的潜在价值,本文结合安路科技FPGA做简单总结,说明基本原理。

2020-12-24 14:28:09 916

916 FPGA可以调用分布式RAM和块RAM两种RAM,当我们编写verilog代码的时候如果合理的编写就可以使我们想要的RAM被综合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

2022-02-08 15:50:49 12183

12183

单口 RAM(Single RAM)、双口 RAM(Dual RAM)、简单双口 RAM(Simple-Dual RAM)、真双口 RAM(True-Dual RAM)有什么不同? 对于 分布式

2021-05-03 09:47:00 7234

7234

RAM :随机存取存储器(random access memory,RAM)又称作“随机存储器”。

2023-04-25 15:58:20 5064

5064

单口 RAM(Single RAM)、双口 RAM(Dual RAM)、简单双口 RAM(Simple-Dual RAM)、真双口 RAM(True-Dual RAM)有什么不同?

2023-06-25 17:47:11 1970

1970

本文主要讲述了Speedster7t FPGA的片上SRAM,也就是Block RAM针对传统的结构所做出的一些优化。

2023-07-13 17:24:15 302

302

设计都涉及到对RAM的读写操作。在FPGA芯片中,RAM也叫做存储块(Block RAM),可以存储大量的数据。 FPGA中的RAM可以一次读取多个数据,这是因为RAM的结构是一个多列的数据表格,其中每一列都是一个包含多个存储单元的块。通过在时钟的一次上升沿来读取RAM中的数据,这个操作必须在一个

2023-10-18 15:28:20 598

598 FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

2024-03-15 13:58:14 81

81

德赢Vwin官网

App

德赢Vwin官网

App

评论