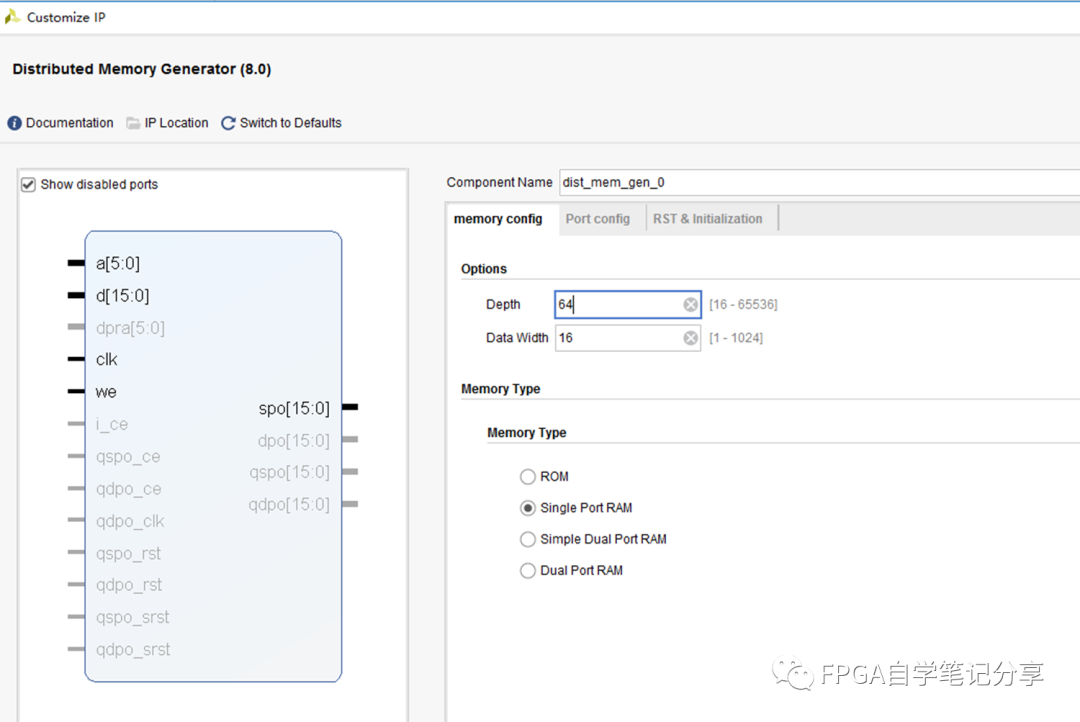

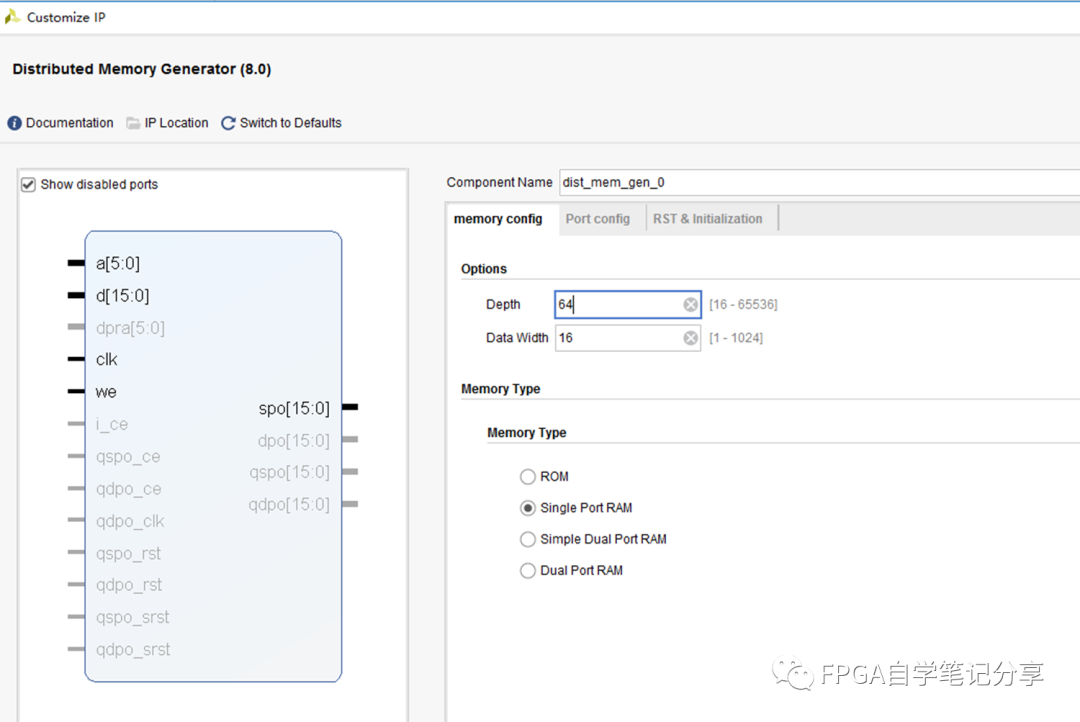

双/双端口 RAM 以及基于 SRL16 的 RAM。该IP的灵活的特性配置方式,使用户能针对存储器类型、数据宽度、存储器大小、输入/输出选项和复位选项进行定制。

2023-11-17 17:00:30 690

690

初始化时存入数据。那在IP核rom中存放大量数据对FPGA有什么影响,比如我想存65536个16位的数,然后在64M或者128M的时钟下读出来。会不会导致FPGA速度过慢?

2013-01-10 17:19:11

的提升。同时也给运算增加了难度,对并行化运算、灵活化运算提出了更高的运算。三、FPGA H.265IP核简介1.性能摘要2.特点H.265帧速率:1fps-60fps支持双流输出支持投资回报率

2019-03-08 10:47:22

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且

2018-08-13 09:27:32

的基础上,给出了一种仿真调试方 案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。1 OC8051结构分析OpenCores网站提供的OC8051 IP核

2012-08-11 11:41:47

FPGA嵌入8051单片机 IP核编程,编写的c语言矩阵键盘程序可以在stc89c54单片机上正常工作,但是下载到FPGA中8051单片机ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

本帖最后由 jf_25420317 于 2023-11-17 11:10 编辑

FPGA开发过程中,利用各种IP核,可以快速完成功能开发,不需要花费大量时间重复造轮子。

当我们面对使用新IP核

2023-11-17 11:09:22

有谁知道现在国内外有哪些公司卖FPGA的图像处理相关的IP核?

2015-04-28 21:34:24

是具有知识产权核的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。到了SOC 阶段,IP 核设计已成为ASIC 电路设计公司和FPGA

2018-09-03 11:03:27

/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个发展趋势。许多公司推荐使用现成的或经过测试的宏功能模块、IP核,用来增强已有的HDL的设计方法。当在进行复杂系统设计的时侯,这些宏功能模块、IP

2011-07-15 14:46:14

参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个发展趋势。许多公司推荐使用现成的或经过测试的宏功能模块、IP核,用来增强

2011-07-06 14:15:52

USB OTG的工作原理是什么?IP设计原理是什么?如何进行IP模块设计?USB OTG IP核有什么特性?如何对USB OTG IP核进行FPGA验证?

2021-04-27 06:44:33

#2024,为FPGA生态加油,为FPGA社区点赞#...使用IP核时如何进行modelsim仿真

2024-02-02 20:22:37

Altera系列FPGA芯片IP核详解

2020-06-28 13:51:01

划分为几个主要模块,分别介绍各个模块的功能,用VHDL语言对其进行描述,用FPGA实现并通过了仿真验证。该IP核具有良好的移植性,可驱动不同规模的LCD电路。 关键词:LCD;驱动电路;IP 引言

2012-08-12 12:28:42

使用LabVIEW FPGA模块中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一个输入。我参考网上VHDL CORDIC IP核,说是将XY合并了,高位X低位Y。不知道在LabVIEW中如何将两个值X、Y合并成一个(X、Y均为定点数)。具体情况如下图:

2019-09-10 20:07:07

本教程的过程中,请读者注意以下几点: 本教程在编写时充分借鉴了周立功编写的mc8051 IP核教程,同时针对其中较为落后的一些内容进行了更新(周立功的教程使用的是Cyclone系列的器件,软件版本也很低

2019-05-24 04:35:33

的SOPC系统中设计了LCD显示驱动IP核,并下载到Cyclone系列的FPGA中,实现了对LCD的显示驱动。

2019-08-06 08:29:14

移位寄存器 (SRL16)”第 8 章 “使用专用多路复用器”第 9 章 “使用进位和算术逻辑”第 10 章 “使用 I/O 资源”第 11 章 “使用嵌入式乘法器”第 12 章 “使用互连”“部分 II

2013-02-27 20:20:10

USB_OTG_IP核中AMBA接口的设计与FPGA实现

2012-08-06 11:40:55

`Xilinx FPGA入门连载73:波形发生器之IP核CORDIC(正弦波)配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2016-04-24 18:57:15

`Xilinx系列FPGA芯片IP核详解(完整高清书签版)`

2017-06-06 13:15:16

在仿真fft ip核时 输出信号一直为0,检查了输入波形,应该没有问题,大家帮忙看看吧输入是由rom里面的mif文件产生的信号。

2017-11-21 10:44:53

我用quartus II调用modelsim仿真fft ip核,仿真结束后我想验证下数据是否正确,结果是:我用matlab生成同样的整形数据,然后用modelsim仿出的结果txt文件与用

2012-09-20 12:48:37

请问哪位高手有ise软件中的各个ip核的功能介绍

2013-10-08 16:41:25

请教各位大神,小弟刚学FPGA,现在在用spartan-3E的板子,想用上面的DDR SDRAM进行简单的读写,用MIG生成DDR核之后出现了很多引脚,看了一些资料也不是很清楚,不知道怎么使用生成的这个IP核控制器来进行读写,希望大神们稍作指点

2013-06-20 20:43:56

modelsim 仿真 altera IP核(ROM,RAM实例)急求大神们ROM和RAM 的综合仿真代码

2015-11-19 21:02:57

- Instantiation Template - mult_gen_0.veo,可以打开实例化模板文件。如图,这段代码就是使用Verilog调用这个IP核的示例代码。2. 将示例代码复制到demo.v文件中,并进行修改

2018-05-15 12:05:13

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

起来就是1001_1001,即为十进制的153。这部分的具体应用将在后面课程数码管的使用一讲中详细阐述。图5-17 两级级联计数值为10的计数器功能仿真波形图至此就完成了一个基本的基本IP使用的流程。请以此为基础自行设计使用其他IP核并进行仿真以及板级验证。小梅哥芯航线电子工作室

2016-12-22 23:37:00

讲,主要通过演示FPGA数字逻辑设计中除Verilog代码方式设计外另外一种最常用的设计方式——使用IP核进行系统设计。本教程讲解了如何在Quartus II软件中调用一个基本的免费IP核——计数器IP核

2015-09-22 14:06:56

内建的示波器。SignalTapⅡ的使用要新建一个仿真调试文件。SignalTapⅡ可以设定信号的触发方式。其他请补充。另,FPGA的IP核并不是只有这几种,从新建IP核的界面可以看到,IP核还有很多。

2016-10-11 22:24:16

通过Quartus II 软件创建PLL IP核。首先,要新建一个工程,这个方法在之前的帖子中已经发过,不会的可以查看前面的相关帖子。创建好自己的工程:打开如下的菜单

2016-09-23 21:44:10

的时钟。首先建立一个文件在ip核目录里搜索ALTPLL然后在工程文件的par文件里建立一个文件夹ipcore将刚刚的变化保存到文件里命名为pll_clk然后点击ok就会出现配置过程界面FPGA系统晶振为

2020-01-13 18:13:48

大家好,我总是使用SRL16作为输入同步器。但是最近我读了这篇文章:http://forums.xilinx.com/t5/Inmplementation

2019-07-25 08:54:39

多核体系结构的硬件仿真平台FPGA资源消耗随计算核数目成线性增加。这里提出的对称多核体系结构FPGA仿真模型,解耦合计算核数目与系统硬件开销的线性关系,其核心设计思想是:在构建仿真系统时,使用一个与目标系统中单个计算

2019-08-23 07:06:56

此时功能出现毛刺,可先不深究。图5-12 计数值为10的功能仿真现在将IP核位数进行更改为二进制计数,打开Mega Wizard插件管理器,选择第二项编辑现有的IP核,并选择先前生成的counter.v

2019-03-04 06:35:13

新手见谅使用IP核设计了一个10阶3级的CIC滤波器,输入数据位宽12位,输出最大22位但是仿真出来的结果有种溢出的感觉,想不通是怎么回事,求各位前辈帮忙分析~~贴出来IP核设置界面,还有matlab处理的结果{:4_108:}

2013-10-13 16:56:12

刚刚接触IP核做FFT,现在用的是FFTV9.0,已经建立了一个IP核,但是如何仿真呢?是用quartus自带软件,还是要用MATLAB?抑或其他?我用的自带软件,但是什么也没有出来。正确的办法应该怎样呢,谢谢指点。

2011-04-21 10:22:31

quartus ii9.0创建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)这些文件都有用吗,想在其他工程里调用这些IP核,这几个文件全部要添加吗?

2013-07-02 17:20:01

最近在做一个FIR低通滤波器,利用Matlab 产生滤波系数,导入到Quartus中,再利用其中的FIR IP核进行滤波器设计,在采用分布式全并行结构时,Modelsim 仿真有输出;如果改为分布式

2018-07-05 08:33:02

最近进行FPGA学习,使用FIR滤波器过程中出现以下问题:使用FIR滤波器IP核中,输入数据为1~256,滤波器系数为,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

在quartus II13.0版本上调用FFT IP核并进行modelsim-altera仿真,在生成IP核时,step2中勾选generate simulation model、generate

2016-10-07 22:23:33

和朋友开发了几个基于 FPGA 的高速存储 IP 核,考虑到工业相机等应用场合需要有文件系统以方便做数据管理,所以将 NVMe 和 exFAT 两大IP核集成一起,可以实现将数据写入SSD后,拔下

2022-06-03 11:35:06

基于FPGA的16位数据路径的AESIP核提出一种基于FPGA 的16位数据路径的高级加密标准AES IP核设计方案。该方案采用有限状态机实现,支持密钥扩展、加密和解密。密钥扩展采用非并行密钥扩展

2012-08-11 11:53:10

基于FPGA的IP核8051上实现TCPIP的设计

2012-08-06 12:18:28

我毕业设计要做一个基于FPGA的IP核的DDS信号发生器,但是我不会用DDS的IP核,有没有好人能发我一份资料如何用IP核的呀。我的浏览器下载不了网站上的资料,所以只能发帖求帮忙了。

2015-03-10 11:46:40

Implement页面中,可以对FPGA存储器或乘法器相关的资源进行选择配置。在配置页面左侧,可以查看IP接口(IP Symbol)、实现信号位宽细节(ImplementationDetails

2019-08-10 14:30:03

产生一组1000个点的余弦数据,存放在time_domain_cos.txt文件中,这组数据将作为FPGA的仿真输入激励,经过FIR滤波器进行滤波处理。clc;clear `all;closeall

2019-07-16 17:24:22

受到业内人士的青睐。本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2019-07-04 06:02:19

此提供了新的解决方案。IP核(IP Core)是具有特定电路功能的硬件描述语言程序,可较方便地进行修改和定制,以提高设计效率[3]。本文研究了基于FPGA的数据采集控制器IP 核的设计方案和实现方法,该IP核既可以应用在独立IC芯片上,还可作为合成系统的子模块直接调用,实现IP核的复用。

2019-07-09 07:23:09

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

【摘要】:Viterbi译码器在通信系统中应用非常普遍,针对采用DSP只能进行相对较低速率的Vit-erbi译码的问题,人们开始采用FPGA实现高速率Viterbi译码。本文首先简单描述了

2010-04-26 16:08:39

:SoC的重要衡量指标。我们在IP核设计阶段就需要将TP核功耗参数进行精确估计并进行相应的功耗优化设计;基于此.本文重点讨论在IC设计过程中IP核的验证测试问题并以互联网上可免费下载的原始IP核资源为例

2021-09-01 19:32:45

如何仿真IP核(建立modelsim仿真库完整解析)

2012-08-15 13:16:12

我正在尝试将Xilinx MIG IP Core从1.7版升级到1.9版。 Coregen UI左侧有一个方便的“升级IP核”按钮,但它显示为灰色。我需要做什么才能进行IP核升级?我在Kintex

2019-11-04 09:26:19

FPGA 架构中的 SRL16 和触发器是通过 GWE(全局写使能)信号来释放的,该信号允许这些同步元件在配置完成后改变状态。GWE 是紧接配置后启动过程的一部分。

2019-09-03 08:10:58

本文在分析OpenCores网站提供的一款OC8051IP核的基础上,给出了一种仿真调试方案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。

2021-05-08 06:22:32

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

怎么才能在嵌入FPGA的IP核8051上实现TCP/IP的设计?

2021-04-29 06:51:27

的其它设计部分尽量不相关。为了满足上述的要求, 在FPGA中嵌入一个比较理想的选择, 而这个即通用又控制简单的IP核最好选择8051微处理器。

2019-08-26 06:27:15

(InputData Width)和数据输出顺序(OutputOrdering)等。第三个Detailed Implement页面中,可以对FPGA存储器或乘法器相关的资源进行选择配置。在配置页面左侧,可以查看

2020-01-07 09:33:53

代码就是使用Verilog调用这个IP核的示例代码。2.1.png (80.87 KB, 下载次数: 1)下载附件昨天 11:35 上传2. 将示例代码复制到demo.v文件中,并进行修改,最终如下

2018-05-16 11:42:55

本人FPGA小白一枚,最近使用到FPGA的IP核遇到一个问题。比如说:某个IP,用于计算sin函数,使用了流水线机制,所有从输入到输出需要20个时钟周期的延时。另外,还有一个IP,从输入到输出需要1

2021-06-19 11:06:07

设计。本人刚刚接触FPGA,对IP核的理解也是一知半解,是说比如我在verilog中,不能使用+,-,*,/,而必须自己亲自设计,只可以用& ,|,!,^这些运算是么?当然我知道IP核远远不止我提到的这些,但是最基本的+,-,/,*肯定都不可以使用是吧。谢谢大家了!

2018-04-06 20:46:11

如题,调用altera公司的FFT IP核,用的是13.1版本,将modulsim仿真的结果输入到matlab画出频谱图,功能仿真结果没有问题,但门级仿真中除了原频率信息外,出现了很多不存在的频率

2018-08-28 20:43:56

(Intellectual Property)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短

2019-07-29 08:33:45

FPGA架构中的 SRL16 和触发器是通过 GWE(全局写使能)信号来释放的,该信号允许这些同步元件在配置完成后改变状态。GWE 是紧接配置后启动过程的一部分。

2011-12-09 15:43:27 914

914 The SRL16E was introduced in the Virtex FPGA architecture and is included in allvariants

2012-02-17 15:03:32 0

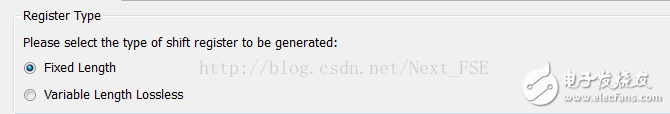

0 可以定义移位长度的移位寄存器。就是用一个lut可以实现16位的移位寄存器。

2017-02-11 11:24:08 6869

6869

基于SRL16的分布式RAM不再支持V5、S6和V6等器件,但是SRL16是所有XIlinx器件都支持的,并且在设计中应用非常频繁,因此可通过调用原语的方法来调用SRL16E甚至SRL32E来实现原来ISE分布式RAM IP核的设计。

2018-05-05 10:38:00 7011

7011 介绍了在大型工业模拟仿真系统中,利用FPGA和软IP核实现数据采集及收发控制的方案,并对其进行设计实现。重点阐述了在发送指令和采集接收两种数据流模式下.该IP核的控制处理逻辑及工作状态机的设计及实现

2018-11-07 11:14:19 20

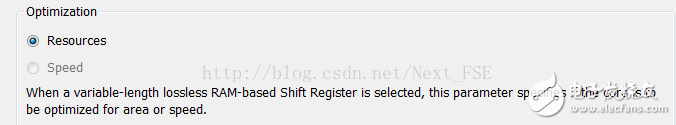

20 SRL(移位寄存器)资源,在FPGA中都有,不过是叫不同的名字。Xilinx FPGA内部的LUT有个特殊功能,就是可以配置成可变长度SRL。

2020-12-31 16:45:35 8

8 up table)查找表实现的话就很轻松了,LUT是通过提前存储下一张真值表来实现逻辑运算的,所以非常节省逻辑资源。常用的移位寄存器SRL种类很多,这里以16bit的SRL16E为例,说一说怎么使用它。

2020-12-31 16:45:34 20

20 核的不同模块进行实体/块的仿真。前文回顾如何测试与验证复杂的FPGA设计(1)——面向实体或块的仿真在本篇文章中,我们将介绍如何在虹科IP核中执行面向全局的仿真,而这也是测

2022-06-15 17:31:20 389

389

德赢Vwin官网

App

德赢Vwin官网

App

评论