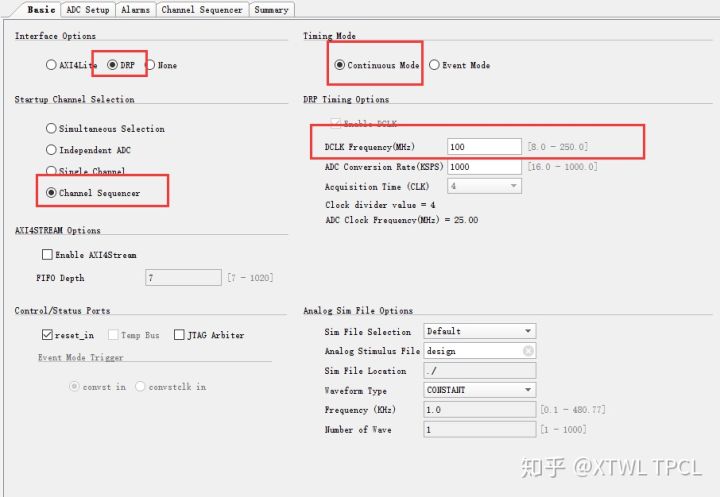

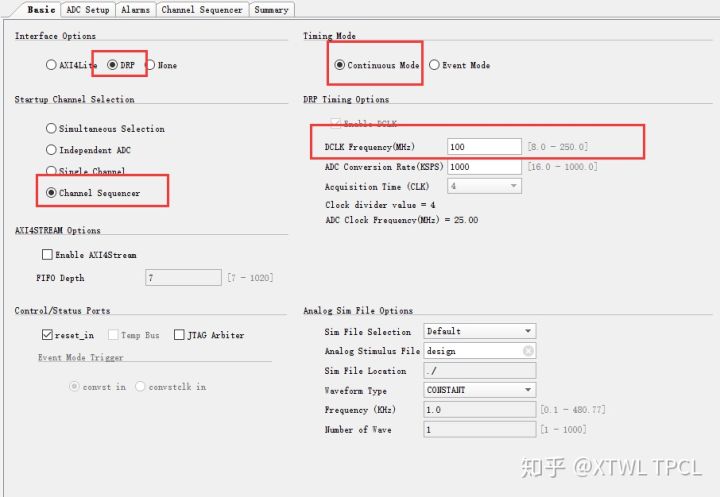

Xilinx 7系列FPGA全系内置了一个ADC,称呼为XADC。 这个XADC,内部是两个1mbps的ADC,可以采集模拟信号转为数字信号送给FPGA内部使用。 XADC内部可以直接获取芯片结温和

2021-01-01 10:58:00 4216

4216

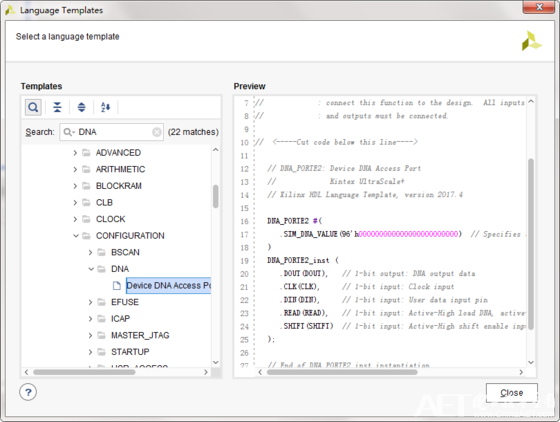

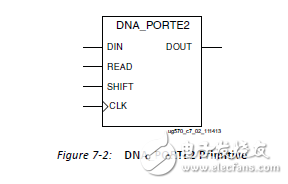

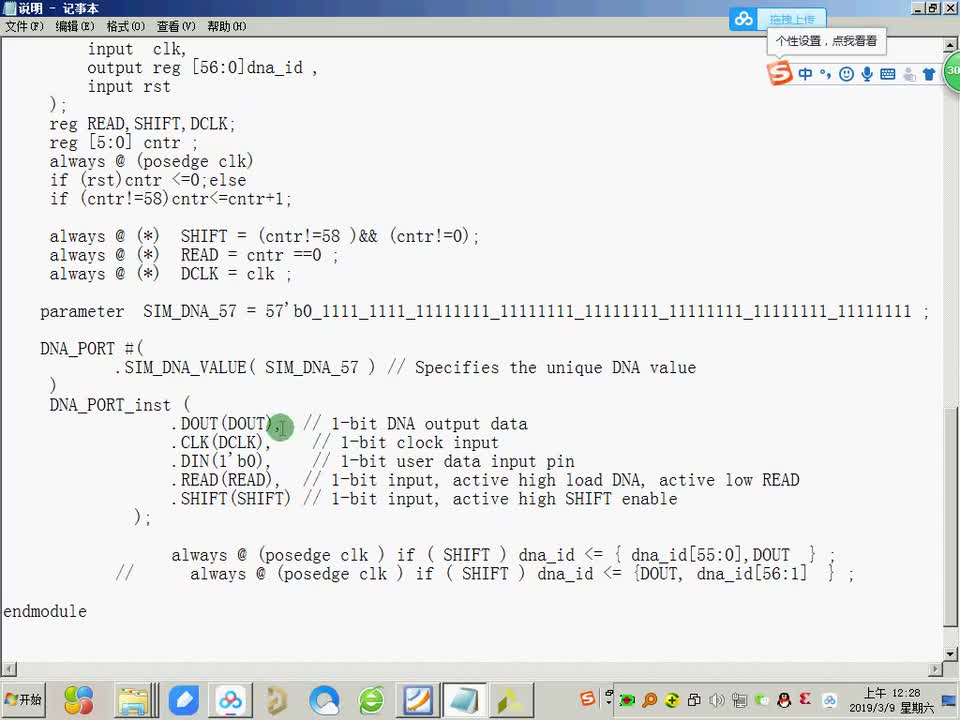

作者:Evening Xilinx每一个FPGA都有一个独特的ID,也就是Device DNA,这个ID相当于我们的身份证,在FPGA芯片生产的时候就已经写死在芯片的eFuse寄存器中,具有不可修改

2021-01-02 09:44:00 4187

4187

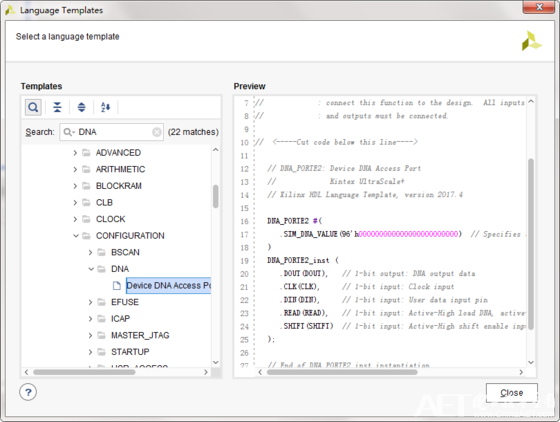

中找到。”但我真的找不到这个模板!我也很喜欢使用项目导航器来实现设计。但我无法找到一个选项生成HDL模板或在IP核生成器中没有DNA或DNA_Port。感谢帮助

2020-06-12 07:53:26

如果采用dna加密,读取每块fpga的id,在允许的范围内就输出使能信号驱动算法模块,就是在开发时将客户提供的id预先存入ram,重新综合成ngc文件给用户。这种方法有几个问题想请教各位

2012-05-02 17:54:53

请教大家,我打算使用这个方案,FPGA使用控制器硬核,外面挂两个16位DDR,这两个DDR的的差分时钟、地址线、控制线等共用,只有数据线使用各自的。希望做到两片同时访问,一次把32位数据分成两个16

2016-04-26 13:41:00

FPGA系统设计中,如果用两个FPGA工作,应该如何设计两片之间的通信?从片的配置和时钟输入与主片有何不同?一个做主片用于数据处理和控制,一个做从片用于IO扩展。硬件和软件上应该如何设计两片之间

2023-05-08 17:18:25

.................................................92.1 理解综合两个过程 ...................................................82 综合工具与代码风格

2012-08-11 11:43:17

请教大家一个问题,板子上有两个FPGA,想用一个PROM配置,将PROM和两个FPGA用边界扫描下载方式连起来可以吗? 就是下图这种模式,可不可以再多串一个FPGA呢?

2014-03-24 15:53:09

的JTAG Chain和Debug Core,因此本文提出一种比较方便的调试方法来同时使用这两个core:ILA通过analyzer查看,VIO通过TCL控制。使用步骤:使用CoreGEN生成VIO

2012-03-08 15:29:11

本本将从常见的XILINX FPGA和Altera 两家FPGA的电源供电作如下介绍:XILINX FPGA:FPGA(FPGA

2021-12-28 06:38:44

和Bottom各一个单端管脚。图1给出了K325T芯片用户Bank IO原理图举例。图1、K325T芯片用户Bank IO原理图在图中,我们可以看到红色圈住的两个单端信号,绿色线条圈住的_CC时钟管脚不用作时钟

2021-05-28 09:23:25

和Bottom各一个单端管脚。图1给出了K325T芯片用户Bank IO原理图举例。图1、K325T芯片用户Bank IO原理图在图中,我们可以看到红色圈住的两个单端信号,绿色线条圈住的_CC时钟管脚不用作时钟

2021-07-08 08:00:00

各位大神,请问Xilinx FPGA中的DCI是如何使用的?我知道是把每个Bank的VRP、VRN管脚分别下拉、上拉,除此之外,在HDL代码和约束中应该如何写呢?查了半天资料没有查到,所以来论坛问问。@LQVSHQ

2017-08-20 20:51:57

`Xilinx FPGA无痛入门,海量教程免费下载 无私的特权同学为您送上85个课时的文档教程,35个经典例程,百度网盘可以免费下载:http://pan.baidu.com/s/1jGjAhEm

2015-07-22 11:49:20

两个文件都可以加载。但 是,当用户在ISE中调用了EDK(比如使用microblaze或者powerpc),ISE生成.bin文件并不会把用户的.elf文件初始化到 FPGA内部的数据和程序存储器中

2016-05-22 23:38:23

frame就会被分开,在配置时无法寻址。 各个模块实现在各自的区域中,那么各模块间的通信是怎样实现的那?在FPGA内信号的传递是通过布线资源实现的,两个模块A、B要实现通信既是将A的信号 线与相映的B

2015-09-22 23:36:50

是怎样实现的那?在FPGA内信号的传递是通过布线资源实现的,两个模块A、B要实现通信既是将A的信号 线与相映的B的信号线相连,由于ise的自动布线无法指定某条信号线布在哪里,所以相邻两个模块的信号线不能

2015-08-20 22:57:10

描述PMP10555 参考设计提供为移动无线基站应用中的 Xilinx® Ultrascale® 16nm 系列 FPGA/SoC 供电所需的所有电源轨。此设计对内核及两个多输出降压型稳压器 IC

2018-11-19 14:58:25

你好,我是与FPGA有关的初学者,但我对以下内容感兴趣:Xilinx Virtex-7 FPGA VC707评估套件我注意到PCIe插座是x8,但我的PC主板只有x16?两个插座兼容吗?问候,鲁道夫

2020-03-17 10:00:32

`描述PMP10555 参考设计提供为移动无线基站应用中的 Xilinx® Ultrascale® 16nm 系列 FPGA/SoC 供电所需的所有电源轨。此设计对内核及两个多输出降压型稳压器 IC

2015-05-11 10:46:35

哪位大神比较熟悉Xilinx的FPGA,本人新手一枚,想学习FPGA,希望能告知一些Xilinx的FPGA快速入门资料获取方法。谢谢!!!

2014-03-11 01:05:57

,编译即可生成如上两个文件,均是先加载.nky然后加载.bit(要妥善保留.nky文件)。完成以上步骤加密设计完成。该方法需要注意如下:1.下载流程首先烧写.nky然后烧写.bit文件2.不支持动态配置

2013-01-01 20:44:47

设置需要以下设备:两台运行Windows®操作系统的标准台式机/笔记本电脑两个Xilinx® VC707开发套件两个AD9625 FMC电路板,AD-FMCADC2-EBZTektronix HFS

2018-09-03 14:48:59

\AD 10\Library\Xilinx目录下仍然只有Xilinx Spartan-3AN.IntLib一个集成库,Altera/Lattice也是如此,如何获取并安装其他期间的集成库啊?谢谢了,有经验的大大请不吝赐教

2012-01-15 10:16:41

的忘了。。。。。。。。。小鱼装个逼给大家小小科普一下这个DNA号是啥东西?Xilinx公司的FPGA芯片都有自己独一的Device DNA号,这个是一个二进制序列,而且每个芯片的都是唯一的。用户可以

2016-06-06 23:44:45

嗨,我需要在我的设计中使用两个BRAM来实现两个FIFO。我知道在spartan6上最大BRAM内存可以是9或18 K,所以我使用64x32bit和512x8bit BRAM,它们一起小于9k。但是

2019-08-05 08:45:37

写了两个FPGA程序,是两个模块,如何将这两个模块连接到一起进行编译仿真。应该如何操作。

2013-06-06 13:40:07

你好。我在我的设计中使用了两个FPGA(Spartan 3)。在这种情况下,我可以使用单个Config PROM将我的位文件加载到FPGA。如果是,我应该如何连接FPGA和PROM,以便相应的配置

2018-09-28 11:36:13

你好,我目前正在研究一个项目,我需要在两个替代设计选项之间做出决定,我必须考虑可靠性分析。(我不需要担心我的设计中的软错误效应)根据我的研究,我发现FIT值是FPGA可靠性的基本标准。在第一个设计中

2020-03-12 11:16:18

基于FPGA产生两个控制脉冲(周期,脉宽,占空比,时序关系可调),用控制脉冲来控制两台工业相机。本人不是很懂,求大神指点。。。

2016-05-30 21:59:54

都可以帮助获取上述两个电源板的信息?谢谢! 以上来自于谷歌翻译 以下为原文I have an HP 6624A system power supply SN 2621A and need a

2019-07-08 11:26:13

;elsif clock_falling_edge 去抖输入 - 使用最后读取值万一但实施失败我还修改了我的时钟pll配置,我创建了两个时钟输出,180度相移第一个时钟上升沿读取输入线,第二个时钟去抖动输入

2019-08-05 06:25:54

我有一台Kintex 7 XC7K325T卡。关于memroy资源的官方用户指南说明我的卡有445个36-Kb BlockRAM块。来自同一指南:“Xilinx®7系列FPGA中的Block RAM

2019-03-05 12:28:54

。我想创建一个sim_tb_top.v来实例化设计的两半(即为不同的FPGA上的每个模块创建两个xdc文件)并编译并模拟设计的sim_tb_top.v。我将如何进行此操作?我应该创建两个项目并在每个

2020-03-17 08:55:38

你好,我打算建立通信以在两个处理器之间读写。一方面是ASIC(MCIMX6)上的四核ARM Cortex A9处理器,另一方面是FPGA(ZC7020)。我在FPGA端没有任何PCIe硬端口。因此

2020-04-16 09:04:30

我需要知道上面的xilinx产品是否只包含两个RS232和一个FPGA(XC3S700A-FG484)和小板上的FLASH PROM(超过4 MB)如果有这样的东西,请告诉我如何获得它,谢谢

2019-09-20 10:33:01

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP产品介绍使用Xilinx的FPGA、SoC和ACAP进行设计和开发

2021-01-22 06:38:47

接口,所以我想问一些问题,如果两个FPGA我选择双工通信,我可以只使用一根光纤(FPGA_2在与FPGA_3通信时从FPGA_1接收数据)吗?或者在一对LC接口中有两个单工,一个接收发送(但是Map一直出错)?

2019-08-07 10:09:05

大家好,如果两个FPGA连接在单个JTAG链中。那么DONE和INIT引脚的推荐连接是什么。两个FPGA的INIT引脚(也是DONE引脚)是应该连接在一起还是应该分开?Xilinx是否为此推荐了任何

2019-01-10 11:00:55

1.工艺节点 首先不管选择什么厂家的产品,都建议在其主流产品中选择合适的芯片。 以上是目前 Xilinx 主流的也是常用的几个 FPGA 产品系列,这里不谈传说中的后两个系列

2020-12-23 17:21:03

为什么属性节点中只能获取buttom(红色游标)的位置,而没有top(黄色游标)的位置,请问游标位置是用cursor.posx、cursor.posy这两个属性获取吗?或者说我获取游标位置的方法不对,请熟悉的朋友指点指点,我再此先行谢过

2014-06-06 22:24:27

你好,任何人:我现在用两块Kintex超大规模FPGA开发单板。我应该如何为两个FPGA供电?1)单一解决方案,一个DCDC稳压器供电两个FPGA的相同电源轨(如VCCINT)。2)单独解决方案

2019-04-03 15:26:53

本帖最后由 eehome 于 2013-1-5 10:09 编辑

共8章,很全面包括altera和xilinx,两个公司的FPGA和相关软件都涉及到,软件操作,语法点,编码风格,还有专门一章

2012-12-06 16:10:55

您好Xilinx社区,我想用两个时钟驱动我的系统。一个时钟用于多个组件,与主时钟一起运行并由IBUFGDS生成。另一个应该驱动IBUFDS_GTE2原语,因为实现了PCI Express。我有两个

2018-11-09 11:41:50

我有一个用于过时的Xilinx FPGA的加载文件。是否有机会将其转换为Xilinx新FPGA的文件?例如斯巴达。以上来自于谷歌翻译以下为原文I have a loading fille fora

2019-02-13 07:53:44

你好,教授们:我有两个相同的FPGA,它们是240t我已经知道测量FPGA的阻抗是一件危险的事情,但我把它们放在同一块电路板上。我测量了每块板的阻抗,发现数据不同。我测量的数据如下:VCCINT

2020-06-17 11:25:59

我正在设计一个带有两个配置为串行菊花链的Spartan 6-LX9的电路板,我想知道一个XCF04S可用于存储两个FPGA的配置。以上来自于谷歌翻译以下为原文I am designing a

2019-07-30 07:43:32

1中的TXOUTCLK信号之间的相位偏移都会发生变化。因此,我无法找到一种方法来在两个FPGA上的TXOUTCLK之间获得一致的相位偏移,这在FPGA被重新编程时会持续存在。我希望有一些方法可以实现

2020-08-28 06:22:25

MAMF-011069集成双开关 - LNA 模块MAMF-011069 是一款双通道模块,包含两个 2 级低噪声放大器和两个高功率开关,采用 5 毫米 32 引脚 QFN 封装。该模块的工作频率为

2023-01-06 11:31:24

十分钟学会Xilinx FPGA 设计

Xilinx FPGA设计基础系统地介绍了Xilinx公司FPGA的结构特点和相关开发软件的使用方法,详细描述了VHDL语言的语法和设计方法,并深入讨

2010-03-15 15:09:08 177

177 Synopsys和Xilinx合作出版业界首本基于FPGA的SoC设计原型方法手册。

2011-03-21 10:26:23 810

810 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA电路原理与系统设计

2012-07-31 16:20:42 11268

11268

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 Xilinx FPGA设计进阶(提高篇)

有需要的下来看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入门教程(二)——Xilinx FPAG开发环境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 45

45 Xilinx所有的FPGA器件都有Device DNA,这是一个57bit的二进制序列,在器件生产的时候烧死到芯片里面,每个芯片都是唯一的。这个序列,用户可以通过JTAG或者verilog(VHD)应用程序直接读出。怎么使用这个DNA,因应用不同可能千差万别。

2019-10-12 17:55:00 1168

1168 文档内容包含基于Xilinx FPGA的开发板代码及原路图,供网友参考。

2017-09-01 11:09:24 20

20 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 FPGA本身是有专门的时钟cell的,以xilinx FPGA为例,就是primitive库中的BUFG。

2018-12-22 15:33:59 1588

1588 在此Xilinx研究实验室演示中,解释了单源SYCL C ++示例以及生成在Xilinx FPGA上运行的硬件实现的方法。

2018-11-20 06:30:00 2918

2918 Xilinx FPGA是支持OpenStack的第一个(也是目前唯一的)FPGA。

该视频快速介绍了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展台上运行每个演示,并使用OpenStack进行配置和管理。

2018-11-23 06:14:00 3322

3322 本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 在FPGA芯片生产的时候就已经写死在芯片的eFuse寄存器中,具有不可修改的属性,因为使用的是熔断技术。

2020-03-29 16:46:00 4387

4387 Xilinx 7系列FPGA概览 文章目录 Xilinx 7系列FPGA概览 1.Xilinx的四个工艺级别 2.Virtex、Kintex、Artix和Spartan 3.7系列特点 4.7系列

2020-11-13 18:03:30 14065

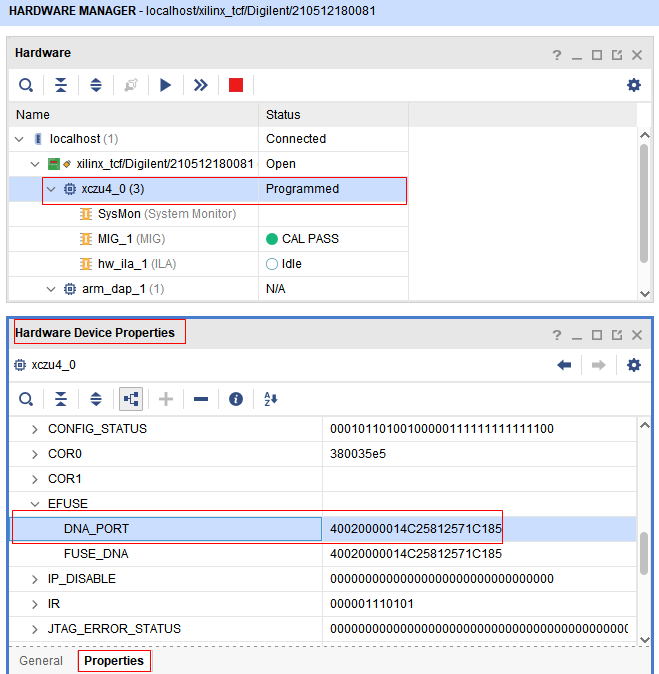

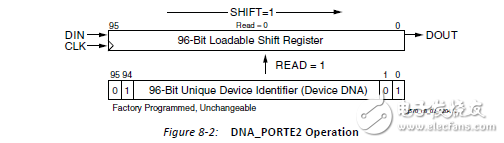

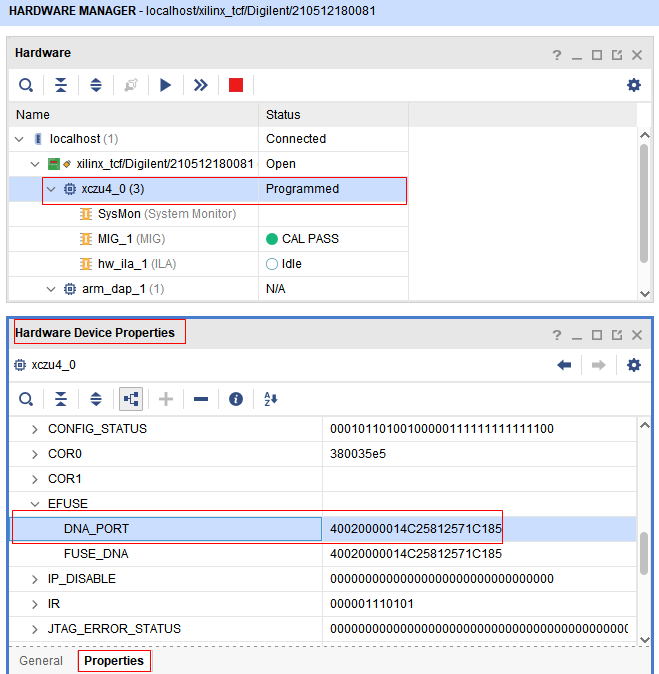

14065 Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

2022-02-08 14:19:49 1149

1149

Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

2021-01-23 06:32:33 10

10 Xilinx-7系列FPGA主要包括:Spartan®-7、Artix®-7、Kintex®-7、Virtex®-7。其性能、密度、价格也随着系列的不同而提升。和前几代FPGA产品不同的是,7系列

2021-01-30 06:00:11 16

16 AD5933 pmod Xilinx FPGA参考设计

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA参考设计

2021-04-22 13:35:23 11

11 AD5628 pmod Xilinx FPGA参考设计

2021-05-19 14:34:17 4

4 AD5541A pmod Xilinx FPGA参考设计

2021-05-19 15:15:19 11

11 AD7193 pmod Xilinx FPGA参考设计

2021-05-19 15:18:13 2

2 AD7091R pmod Xilinx FPGA参考设计

2021-05-19 18:31:59 7

7 AD7156 pmod Xilinx FPGA参考设计

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA参考设计

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA参考设计

2021-05-24 10:29:20 17

17 Xilinx FPGA开发实用教程资料包免费下载。

2022-04-18 09:43:46 24

24 Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

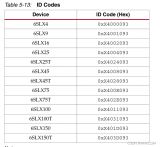

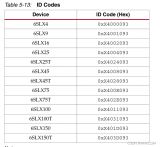

0 ,这样就可以通过读取IDCODE,来进行自动区分不同的硬件,分别进行不同的处理方式。本文介绍Xilinx所有FPGA芯片型号IDCODE的获取方法,一共4种方式,总有一种适合你,这些方法同样适用于别的厂家的FPGA/MCU,比如Intel,Lattice,Microchip等等。

2023-07-03 13:01:31 1583

1583

德赢Vwin官网

网站提供《面向Xilinx FPGA和SoC的超快设计方法指南.pdf》资料免费下载

2023-09-14 10:02:31 1

1 德赢Vwin官网

网站提供《Xilinx FPGA和SoC的超高速设计方法指南.pdf》资料免费下载

2023-09-14 09:41:06 0

0 Xilinx是一家专业的可编程逻辑器件(PLD)厂商,其产品包括FPGA、CPLD、SOC等。Xilinx的FPGA产品线有多个系列,其中7系列和Ultrascale系列是比较常见的两种。那么,这两个系列有什么区别呢?

2023-09-15 14:44:54 1776

1776

每一片芯片内部存有一个设备标识符,xilinx把它叫做DNA,这个DNA是不可更改的,永久存在芯片里面的。

2024-01-03 09:19:03 641

641

Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 215

215

德赢Vwin官网

App

德赢Vwin官网

App

评论