为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定FIFO深度的方法。对FIFO不同深度的实验表明,采用该方法设定的FIFO深度能够比较好地满足系统对数据连续传输的要求。研究结果对深入展开研究和工程设计具有一定的指导意义。

引言

数据进入FPGA的速率高于传出的速率,持续的传输会造成数据的溢出,断续的传输可能会造成数据不连续。使用基于LabVIEW FPGA的DMA FIFO作为主控计算机和FPGA之间的缓存,若DMAFIFO深度设置的合适,FIFO不会溢出和读空,那么就能实现数据输出FPGA是连续的。

本文在介绍了LabVIEW FPGA模块程序设计特点的基础上,结合DMA FIFO的工作原理,提出了一种设定FIFO深度的方法,解决了FIFO溢出、读空的问题,实现了数据的连续传输。实验结果表明该方法正确、可行,程序设计满足系统对数据传输连续性的要求。

1 LabVIEW FPGA模块

LabVIEW FPGA是LabVIEW的一个子模块,使用该模块可以通过图形化的编程对NI公司RIO(Reconfigurable I/O)设备上的FPGA进行配置。图形化的程序直接在硬件上实现,通过对RIO设备上的I/O接口的控制,可以灵活地对I/O信号进行分析和处理,表现出比固定I/O硬件更加优异的特性。使用LabVIEWFPGA模块开发出来的系统具有开发周期短、结构模块化、升级方便等优点。例如,图1表示了一个用LabVIEW FPGA模块设计的程序,在FPGA上实现方波发生器。该方波发生器通过数字接口DIO_1输出方波,其占空比和周期可调。LabVIEW FPGA模块在程序的设计与实现上都展现出了极大的灵活性。

1.1 LabVIEW FPGA程序开发流程

使用LabVIEW FPGA模块开发应用程序的流程如图2所示。首先创建FPGA vi,之后用FPGA设备仿真器在主控计算机上运行程序,反复地调试、修改,直至程序正确无误。然后编译FPGA vi,并把程序下载到FPGA上。FPGA部分的程序完成后,再根据需要在主控计算机上创建用户界面程序Host vi,最终就完成整个系统的设计。

FPGA设备仿真器的打开方法是:首先在“项目浏览器”窗口中的打开“我的电脑”子菜单,右击子菜单中的“FPGA Target”并在快捷菜单中选择“Execute vion”下一级子菜单中的“Development Computer with Simulated I/O”。然后再在FPGA vi中点击“Run”按钮,这时程序在FPGA的设备仿真器上运行。

1.2 开发FPGA vi

发应用程序的第一步是创建用于配置PXIe-5641R板载FPGA的程序。在FPGA vi中可以实现算法逻辑,包括信号同步,定制数字通信协议,板载控制和预警处理判决机制等功能。通过LabVIEW FPGA模块,可使用LabVIEW开发环境和许多类似的功能。但是由于FPGA不支持浮点操作,所以LabVIEW FPGA模块较之LabVIEW完整Windows版开发软件缺少了一些操作符和分析函数。另外,由于PXIe-5641R板卡没有硬盘和操作系统,因此不支持文件I/O和ActiveX功能。LabVIEW FPGA模块的函数面板如图3所示。

硬件对象不管是FPGA设备还是FPGA仿真器,都可以访问LabVIEW FPGA函数。仿真器使用RIO设备的I/O接口,可在主机处理器上执行逻辑算法。检验vi设计中的一些简单性错误,避免不必要的反复编译,尤其是在程序比较大的时候可节省大量的时间,提高编程效率。也可使用仿真器验证vi的执行流程,但无法验证硬件的确定性,若需要验证硬件性能的确定性,必须对FPGA vi进行编译。与其他FPGA开发工具一样,根据应用程序的复杂程度和计算机资源的不同,编译步骤可能要花上几分钟到几个小时的时间。

1.3 开发Host vi

在FPGA vi完成调试、编译、下载到板卡之后,就需要在主控计算机上创建一个用户界面程序Host vi。在用户界面应用程序中可以完成一些实时性要求不高的操作,例如配置系统参数,管理数据等。Host vi通过FPGA接口函数与FPGA vi进行通信,以及处理中断。FPGA接口函数面板会在安装LabVIEW FPGA模块之后,自动添加到LabVIEW的函数面板中。LabVIEW函数面板中的FPGA接口函数面板如图4所示。

2 不同时钟域的数据连续传输

本文中的中频信号生成系统是将主控计算机vwin 生成的数据通过FPGA送到AD9857发送出去。数据进入FPGA的速率为52 MB/s,由于计算机的非实时性呈现断续的形式,其实际的速率要低一些;数据传出FPGA时,其数据位宽为16 b,输出频率为10 MHz,固其持续传输速率为20 MB/s。数据进入FPGA的速率高于出FPGA的速率,这就造成数据在不同时钟域之间传输的问题。为了避免数据的溢出和保证数据连续性,本文使用DMA FIFO作为主控计算机与FPGA之间的缓存。它的存储空间包括两部分:一是主控计算机部分,主控计算机开辟一块内存作为FIFO缓存;二是FPGA部分,FIFO占用部分Block Memory资源作为缓存。二者共同组成一个完整的FIFO,通过PXIe总线传递数据。FIFO的传输机制是:主控计算机首先把一个数组的数据存入作为FIFO缓存的内存中;DMA控制器会自动查询FPGA上的FIFO剩余空间,当满足缓存剩余空间大于数据块容量的条件时,控制器通过PXIe总线把整个数据块一并送入FPGA上的FIFO中;FPGA FIFO再将数据顺序送出。

若在主控计算机向FIFO两次写入数据的间隔期间,FIFO中的数据保持不被读空,就能保证输出FPGA的数据是连续的。而合适的FIFO深度是FIFO不被读空的基础,所以确定FIFO深度的设定方法是数据在不同时钟域之间实现连续传输的关键。

3 FIFO深度的设定方法

3.1 FPGA FIFO深度的设定

DMA控制器将数据从主控计算机内存整块的传送到FPGA的FIFO缓存中,所以FIFO的深度要大于数据块的大小。LabVIEW FPGA里块存储FIFO是以2 KB大小来应用的。DMA FIFO使用RIO设备可获取的内置RAM来存储数据信息,该存储空间与内存读/写是共享的。所以要留一部分RAM空间进行内存的读/写,FIFO的最大值为RAM容量减去16 KB。PXIe-5641R的RAM的容量是1 098 KB,所以,FPGAFIFO的深度设定范围为2~1 082 KB。

另一方面,实际上LabVIEW为了能使FPGA高效运行,对Block Memory方式FIFO的大小作了规定,其大小只能为2M-1(数据由FPGA传向主控计算机)或2M+5(数据由主控计算机传向FPGA),M为数据的地址宽度;当设定值不是这些标准值时,LabVIEW会自动的放大到距其最近的一个标准值。这样就确定了FPGAFIFO的深度,但是还不能保证数据能够连续输出。

3.2 主控计算机FIFO深度的设定

由于对主控计算机内存部分FIFO的读/写是以数组形式断续进行的。所以,数组的长度和两次写入的间隔时间是能否保证数据连续性的重要参数,同时考虑到数据输出FPGA是连续且频率固定的。根据FIFO不读空的原则推测:当写入内存的数组的长度N与数据写入内存的时间T和数据输出FPGA的频率F之间满足如下的关系时,就能做到数据的连续传输:

N/T》F (1)

鉴于主控计算机操作系统的非实时性,需要将主控计算机FIFO深度D的大小设定为N的若干倍;通过大量实验并与NI工程师讨论,确定当FIFO的深度D的大小为N的3~5倍时,可完全满足数据连续传输的要求。

3.3 实验验证

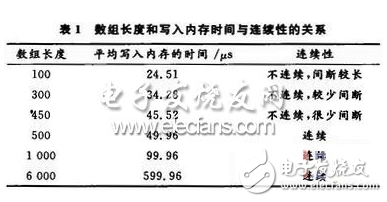

数据写入内存的时间与主控计算机运行速度以及数组的大小有关。表1所示的是数组长度和写入内存的时间与输出数据连续性之间关系的实验结果。其中,平均写入内存时间指的是同一个数组循环执行写入操作10万次得到的平均结果。输出FPGA的速率为10 MHz。

当数组长度较小时,单位时间内写入到内存中的数据较少,内存里的数据不能满足FPGA FIFO读取数据的需求,在下一组数据到达之前内存里的数据已经读空,故输出的数据不能连续。当数组长度增大之后,单位时间写入到内存的数据量也随之增大,内存里的数据能够满足FP-GA FIFO读取数据的需求,在内存读空之前把下一组数据送入了内存,所以输出的数据能够保持连续性。实验结果验证了上述推测公式的正确性。

4 数据连续传输的LabVIEW实现

在本文中系统软件包括两部分:Host vi和FPGAvi,二者是独立而又有联系的两个部分。Host vi运行于主控计算机上,FPGA vi运行于FPGA上,二者通过FIFO来传输数据。

4.1 FPGA程序设计

使用图形化的编程环境LabVIEW FPGA模块来定义FPGA逻辑,除了具有上述的优点以外,LabVIEW作为一种并行结构的编程语言,非常适用于FPGA的并行结构,能够十分方便地实现多线程并行任务。

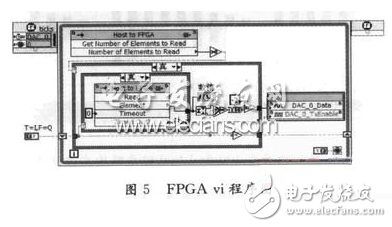

当FPGA vi开始运行时,从Host vi读取数据的FIFO需要一定的初始化时间,时间长度与FIFO的深度成正比。在初始化期间FIFO输出一系列的无效默认值。为了不让无效值进入到下一级的运算中,在DMA方式的FIFO之前加了一个FIFO函数——Get Number of Element to Read,该函数用于获得FIFO内有效数据的数量。当有效数据的数量大于0时,再开始进行下一级运算。考虑到FPGA有限的硬件资源和FPGA FIFO最小值的限制,将数据的地址宽度设为M=11,根据上文分析DMA FIFO的深度设为2M+5=2 053 KB。

4.2 主控计算机程序设计

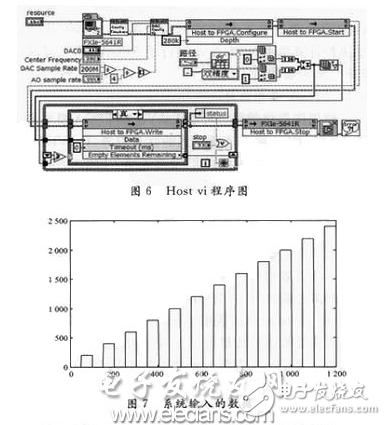

Host vi是系统程序的另一部分部分,它具有建立硬件对象(FPGA)、与硬件通信和图形显示等功能。主控计算机程序图如图6所示,首先要建立与之进行通信的硬件对象,即FPGA;其次配置系统时钟、输出模式;再次创建FIFO,设置其在主控计算机部分的FIFO深度;然后从电子表格读取数据,并循环查询FIFO剩余空间的大小,当剩余空间大于数组长度时,数据写入FIFO当没有足够的空间时,数据保留到下一个循环,满足条件后再写入FIFO;最后关闭FIFO应用,处理错误。

当输入数组长度分别为300和1 000,形状如图7所示的波形时,输出数据的波形如图8所示。由于AD9857上变频的原因,使得输出波形在输入的矩形包络中带有载波,载波频率为60 MHz。根据表1中的数据可以得出结论:此处的编程和上述实验的结果是一致的,即FPGA输出频率为10 MHz,数组长度大于500时,系统数据的输出是连续。同时此结果也表明本文中的LabVIEW程序实现了数据的连续传输。

5 结语

通过设定合适的FIFO深度,实现了数据的连续传输,为后续的工程设计奠定了基础。该设定FIFO深度的方法也对其他使用LabVIEW FPGA模块的工程设计具有一定的参考价值。

德赢Vwin官网

App

德赢Vwin官网

App

评论