赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

2013-07-23 09:25:53 19707

19707

以下是笔者一些关于FPGA功耗估计和如何进行低功耗设计的知识。##关于FPGA低功耗设计,可从两方面着手:1)算法优化;2)FPGA资源使用效率优化。

2014-12-17 09:27:28 9177

9177 7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2022-07-25 10:13:44 4067

4067 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 655

655

FPGA 管脚分配需要考虑的因素FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 10:27:54

解决方案工具包。它的主要工作是由软件来自动生成、优化FPGA芯片的管脚分配,提高FPGA/PCB设计的工作效率和连通性。FSP完成两项重要工作:一、可以自动生成FPGA芯片的原理图符号(symbol

2011-10-18 11:44:31

FPGA 如何估算程序所需的资源?是不是要把输出接到FPGA的PIN上后build,才算是程序所需的资源?因为我有个比较复杂的程序,没有output到FPGA上,LUT使用为8000+一旦output到FPGA上,LUT使用为8W+.是不是此时的LUT使用量才是程序真正所需的?

2017-01-19 09:09:19

FPGA管脚分配需要考虑的因素 FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 11:34:24

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从

2017-03-25 18:46:25

FPGA管脚分配需要考虑的因素.pdf

2012-08-20 19:23:04

FPGA的管脚主要包括:用户I/O(UserI/O)、配置管脚、电源、时钟及特殊应用管脚等。其中有些管脚可有多种用途,所以在设计FPGA电路之前,需要认真的阅读相应

2019-09-18 07:34:49

)是两种不同的硬件实现方式。

FPGA是一种可编程逻辑器件,其内部资源可以根据需要进行配置和重新配置。这些资源包括但不限于:

逻辑单元(Logic Cells):这些是FPGA的核心计算资源,可以实现各种

2024-02-22 09:52:22

各位大神,小弟最近在做一个项目,由于之前选用的FPGA资源不够,现在需要将程序的资源占用率降下来。经过我的冥思苦想,也找不到好的方法,不知道各位大神平时工作中降低资源利用率的方法有哪些?求助啊!!!!

2015-04-04 00:32:57

嗨,我想知道通过使用c ++代码是否存在使用FPGA资源的肮脏,快速且非常粗糙的想法?我的任务是在FPGA上实现一个非常复杂的c ++算法。 c ++代码非常复杂,需要几周或几个月才能理解,但同时

2019-03-26 06:42:03

的GC_CLKPIN,PAR就会报错,反之,当一个信号分配的是GC_CLK PIN,无论是否扇出足够大,都会加入IBUFG,这也其实是FPGA内部结构造成的,只有全局管脚上有IBUFG,所以只要该信号用了全局管脚

2019-07-09 08:00:00

FPGA共享重要资料希望大家互相学习!

2013-05-12 17:28:41

求FPGA内部资源{:soso_e100:}相关资料,发lishenghhuc@126.com,谢谢

2012-09-27 16:55:44

Buffer,支持施密特触发器的磁滞功能。20/26. nCONFIG专用的输入管脚。这个管脚是一个配置控制输入脚。如果这个脚在用户模式下被置低,FPGA就会丢失掉它的配置数据,并进入一个复位状态,并将所有

2014-12-29 11:46:33

对FPGA学习好的资源有哪些?从入门到精通,大家可以分享一起学习呀

2024-01-28 17:00:27

请问FPGA的资源使用如何评估?

2024-02-22 09:55:53

FPGA验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑

2024-01-10 22:40:14

FPGA设计管脚分配注意点

2012-08-11 16:10:10

FPGA设计重要思想个人感觉一般,是个培训ppt,但是思想还是要有的

2014-11-14 17:39:17

FPGA设计的8大重要知识点,你都get了吗?

2021-02-03 07:39:08

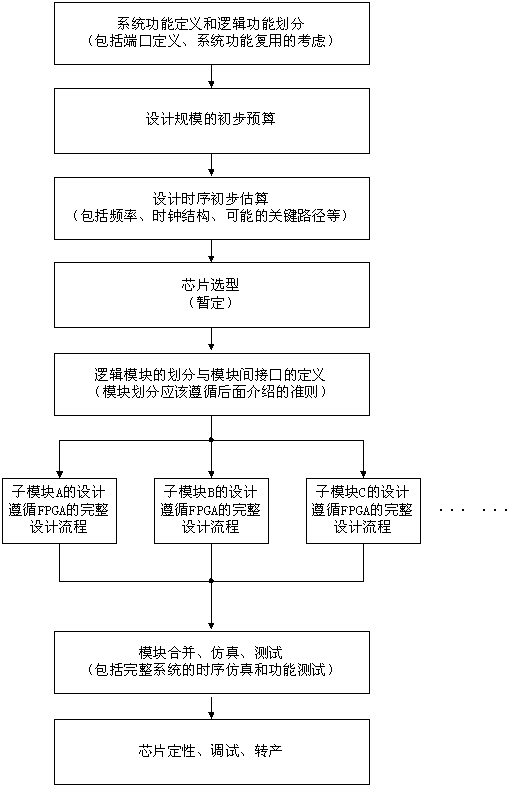

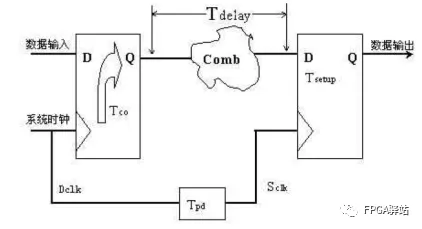

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-07-25 11:09:06

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-07-26 14:47:48

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-11-22 10:04:03

`1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-07-04 14:16:15

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-07-09 14:34:18

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-08-10 14:51:33

`1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2021-07-09 14:24:42

1. 面积与速度的平衡与互换这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数

2020-08-02 10:45:07

我是学单片机的,想问问各位,学习FPGA有没有类似51那种基础的入门途径,语言方面我了解一点verilog,编写程序都是根据芯片资源和实际应用来考虑,那么有没有一种基础的原理讲解或者是适合入门的书籍?主要关于硬件方面的

2013-04-05 15:58:49

关于FPGA芯片资源介绍不看肯定后悔

2021-09-18 08:53:05

最近在用一款松翰的自带ADC资源的单片机,他的有两个管脚的功能是‘’GPIO、ADC: external low reference voltage‘’“GPIO、ADC: external

2019-02-19 10:37:09

ARM在片上资源确定的情况下,能否具备类似FPGA自由分配管脚功能的能力?比如说集成UART的TX/RX可以分配到任意管脚,而并不是只能分配到指定的几个管脚?谢谢

2022-08-01 14:17:49

Quartus II 下FPGA管脚锁定在新建工程、编辑文件、编译、排错完成后就进入管脚锁定以及电平设置阶段。这里还是以一位全加器为例介绍管脚锁定。开发板使用FII-PRA006. 开发工具

2021-07-30 15:09:59

、摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总。 二、管脚分配方法FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按钮

2018-07-03 12:56:11

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-07-08 08:00:00

我用xilinx spartan-6fpga 它硬核的管脚是固定的还是可配置的我在xilinx提供的文档里找不到关于硬核管脚的分配求指导

2012-08-11 09:28:44

⑴ 结合Xilinx、Altera 等公司的FPGA 芯片,简要罗列一下FPGA 内部的资源或专用模块,并简要说明这些资源的一些作用或用途。(至少列出5 项,越多越好)⑵ 如果,对内部特定资源,曾有

2012-03-08 11:03:49

器件、一些存储设备和一些电气接口匹配电路的解决方案已成为主流选择方案。根据多年的应用经验,相关数字系统中,FPGA器件的选型非常重要,不合理的选型会导致一系列的后续设计问题,有时甚至会使设计失败;合理

2012-02-22 13:58:51

右键然后点击 show IO banks,这个时候就会看到FPGA的管脚被几种颜色划分开了。一种颜色下的IO口代表一组bank。你在吧管脚的locaTIon约束完成以后。IO Bank会自动填充完毕

2019-04-03 07:00:00

器件中的重要创新之一,2D NoC 为 FPGA 设计提供了几项重要优势,包括:· 提高设计的性能,让 FPGA 内部的数据传输不再成为瓶颈。· 节省 FPGA 可编程逻辑资源,简化逻辑设计,由

2020-09-07 15:25:33

在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是

2015-01-06 17:38:22

需要做一个FPGA的调研需要FPGA资源如下:速度能到100M,可用IO管脚200-300最好,RAM空间10KByte,表贴封装最好是单一电源供电,xilinx最佳希望大虾们给个建议,谢谢了,论坛新手,只有1E币,再次感谢!

2012-05-29 23:29:57

逻辑结构之上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了大约高达27Tbps的超高带宽。作为Speedster7t FPGA器件中的重要创新之一,2D NoC为FPGA

2020-10-20 09:54:00

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。

2019-09-18 08:26:21

(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析

2019-06-17 09:03:28

,比如时钟域、模块复用、约束、面积、速度等问题,在系统上模块的优化最为重要。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加丰富。FPGA/CPLD一般是由底层可编程硬件单元、BRAM、布线资源

2020-09-18 10:32:44

都会有新的理解和收获。现在在看USB通信。个人总结一下,时序很重要,最起码对我这个初学者很重要,看懂了时序就完成了一大半,我的目的是完成功能,而不是去做到资源和速度的综合优化。所以希望大家要看工作方式

2014-11-05 22:39:10

现在设计FPGA电路,想用EP4CE40F484,可是数据手册里没有A1、B2······这些管脚的定义,想请问一下FPGA管脚定义改怎么看啊?

2018-03-29 10:53:04

比如我设计一个用FPGA控制SRAM写入和读入数据的小程序。但是明明看着SRAM的几个管脚是输入端啊,别人写的都是output类型。这是怎么回事啊,望大神们给点建议,我刚刚入门。

2015-10-13 12:06:46

请问各位学友,站内有没有FPGA视频学习资源,,以及下载quartus具体指南,,,谢谢

2015-08-03 16:11:02

某个 FPGA 的某个 Bank,直接跳转到 PCB 中相对应的 Bank 管脚高亮,这时可以在某一机械层添加标注,进行标记,如图 12-2 所示。图 12-2Bank 的标记(2)按照相同的操作方法

2020-04-26 07:00:00

请问目前资源丰富的一款CPLD或FPGA是什么?

2013-03-22 00:18:27

小弟最近在研究FPGA时钟资源的手册,遇到一个问题想请教各位大神。在Virtex6系列FPGA中,Bank分为top层和bottom层,请问我怎么查看一个Bank到底是在top层还是在bottom层

2015-02-10 10:30:25

ALTERA FPGA 特殊管脚说明、

管脚名称 器件系列 使用模式

2010-06-11 12:29:47 27

27 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证

2011-01-25 18:19:39 163

163 本文简要的分析FPGA芯片中丰富的布线资源 。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。

2012-12-17 17:28:41 3491

3491 电子专业单片机相关知识学习教材资料——FPGA片内资源设计指导

2016-08-23 15:55:35 0

0 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚,不能用N类型管脚等等。

2017-02-11 03:48:34 10684

10684

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类

2017-12-05 11:48:44 8

8 渠道作为企业最重要的资源之一,直接影响企业的营销绩效和经营稳定性,从而影响企业持久竞争优势的确立和保持。畅通的销售渠道可以保证产品顺利进入市场,反之渠道障碍会影响企业市场运作。对众多安防企业和行业渠道研究表明,“销售渠道瓶颈”问题是制约企业发展的普遍问题。

2018-09-03 16:10:22 1192

1192 了解如何描述Spartan-6 FPGA中可用的基本片和I / O资源。

2019-01-04 10:32:00 3056

3056 在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源。

2019-02-15 15:09:05 3580

3580 在使用 FPGA 过程中,通常需要对资源做出评估,下面简单谈谈如何评估 FPGA 的资源。 FF 和 LUT 的数目:这个在写出具体代码之前,初学者通常没法估算,但资深 FPGA 工程师会估算

2020-12-28 07:59:00 8

8 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 15

15 DDR3。 2.FPGA架构设计问题 我们知道,FPGA片上分布着各种资源,如时钟,serdes,RAM,LUT,IO等。在进行FPGA规划时候,应当需要知道项目设计需求,以及需求各模块之间的数据交织情况,这样可以避免

2021-01-07 10:15:31 4645

4645

1. 面积与速度的平衡与互换

这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑

2022-02-10 13:46:37 1011

1011

介绍IO口与FPGA管脚对应关系表。

2021-03-18 10:02:26 12

12 是最佳的,然后通过使用适当的I/O和时钟缓冲器来访问这些时钟路由资源。该章节包括: 时钟缓冲选择考虑 时钟输入管脚 1.时钟缓冲器选择考虑 7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求

2021-03-22 10:16:18 4353

4353

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到:

2021-05-01 09:47:00 10367

10367

引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2021-04-27 10:36:59 3126

3126

(06)FPGA资源评估1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA资源评估5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 面积通常指一个设计消耗FPGA/CPLD的逻辑资源的数量,通常用可消耗的FF(触发器)和LUT(查找表)来衡量。速度指设计在芯片上稳定运行所能达到的最高频率,这个频率由设计的时序状况来决定,以及设计满足的时钟要求

2022-02-16 16:21:28 855

855

这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数。

2022-10-17 17:50:17 637

637 关于 FPGA 的 IO资源分析共分为三个系列进行具体阐述,分别为: IO资源:分析FPGA IO资源的电气特性; IO逻辑资源:分析FPGA的输入输出数据寄存器、DDR工作方式、可编程输入延时

2022-12-13 13:20:06 1099

1099 FPGA中关于SPI的使用

2023-04-12 10:13:16 531

531 本文主要用来随意记录一下最近在为手头的FPGA项目做约束文件时候遇到的一点关于FPGA专用时钟管脚相关的内容,意在梳理思路、保存学习结果、以供自己日后以及他人参考。

2023-08-07 09:20:25 1539

1539

FPGA的BRAM和LUT等资源都是有限的,在FPGA开发过程中,可能经常遇到BRAM或者LUT资源不够用的情况。

2023-08-30 16:12:04 949

949

德赢Vwin官网

App

德赢Vwin官网

App

评论