资料介绍

描述

1. 背景

1A。概述

一个演示来说明:

(1) 创建/封装用于 SoC 设计的可编程逻辑 (PL) 的定制 IP

(2) 从 SoC 处理器系统 (PS) 执行内存映射寄存器写入/读取操作

我在这里使用了一块带有 Zynq FPGA 的 MiniZed 板,但这些概念适用于任何 SoC 设计。虽然这些都是比较基础的概念,但还是有很多的看家步骤和设置。我使用 Vivado/Vitis 2020.2,但早期版本的 Vivado/SDK 的步骤也应该非常相似。

根据需要使用下面的大纲跳过;大胆的步骤突出了关键的设计项目。

1B。大纲

一、概述

2. Vivado - SoC 项目设置

2A。新项目创建

2B。块设计设置

2C。自定义 IP 设置:指定 AXI 接口和内存映射寄存器

3. Vivado - IP 编辑器项目

3A。Verilog Adder:加法器模块的规范

3B。打包IP

4. Vivado - SoC 项目实施:在基础项目中使用加法器

5. Vitis - 应用项目设置

5A。最初设定

5B。创建一个随机数加法应用程序:C代码和解释

5C。运行应用程序:通过 UART 查看结果

六、分析与结论

2. Vivado - SoC 项目设置

2A。新项目创建

1) 打开 Vivado。点击create a new project,给它一个名字(例如ps_pl_demo),然后点击next。

2) RTL Project -> 不指定来源,点击next。

3) 从 Boards 选项卡中选择您的板*,单击下一步,然后单击完成。

* 对于首次设置,您可能需要开发套件的电路板定义文件。Minized位于“技术文档”->“电路板定义文件”下。如果需要,下载并解压缩该文件。开发板的顶级目录(本例中为minized/ )必须复制您的 Vivado 安装目录(例如/home/user/Applications/Xilinx/Vivado/2020.2/data/boards/board_files/ )。

2B。块设计设置

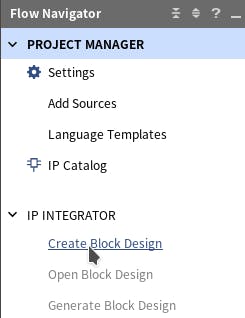

1) 完成 Vivado 的新项目 GUI 后,您将进入标准项目摘要页面。从 Flow Navigator 窗格中单击 Create Block Design。

2) 出现一个弹出窗口,要求输入块设计名称:默认名称就可以了。

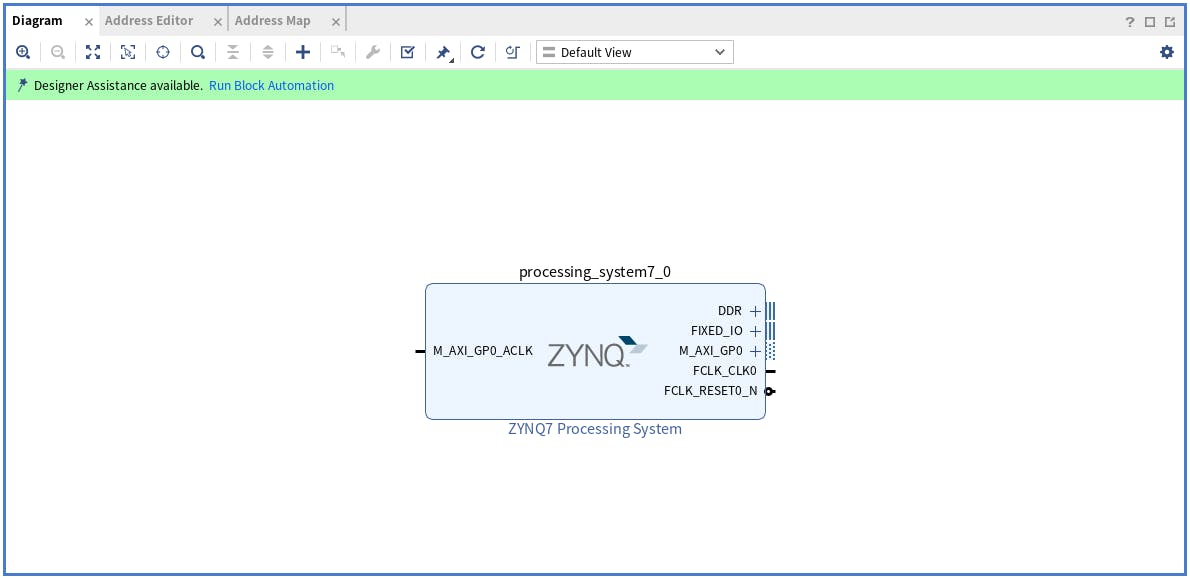

3) 现在出现“图表”窗格。单击“+”按钮并在弹出菜单中双击“ZYNQ7 处理系统”。出现 PS 块:

2C。自定义 IP 设置

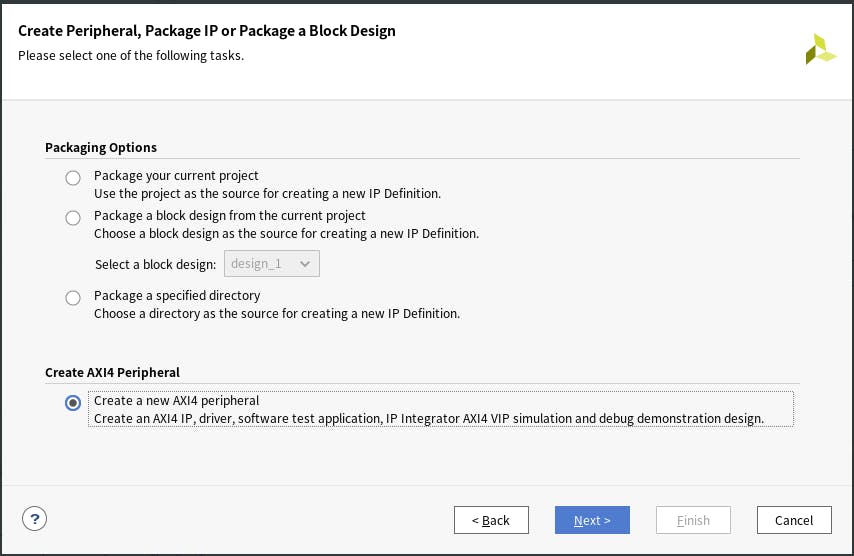

1) 现在,从顶部菜单栏中,单击“工具 -> 创建和打包新 IP”。单击下一步,然后在以下屏幕上单击“创建新的 AXI4 外围设备”并再次单击下一步:

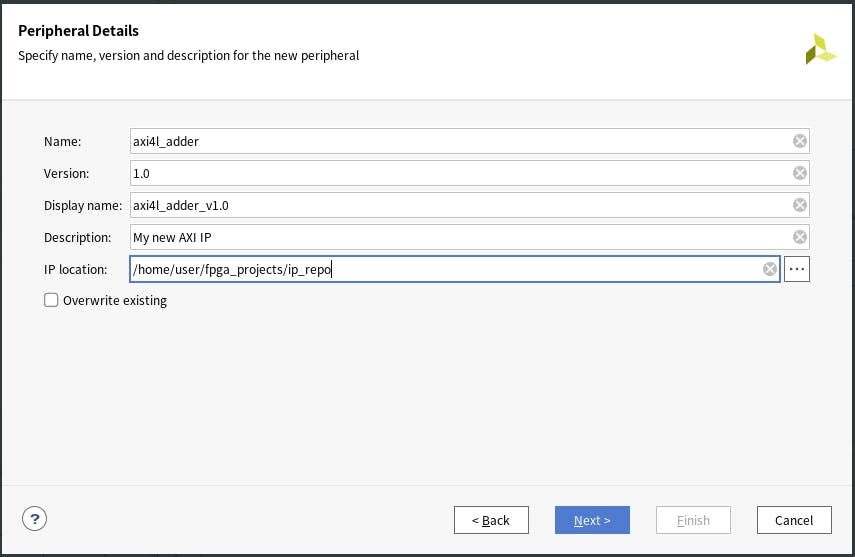

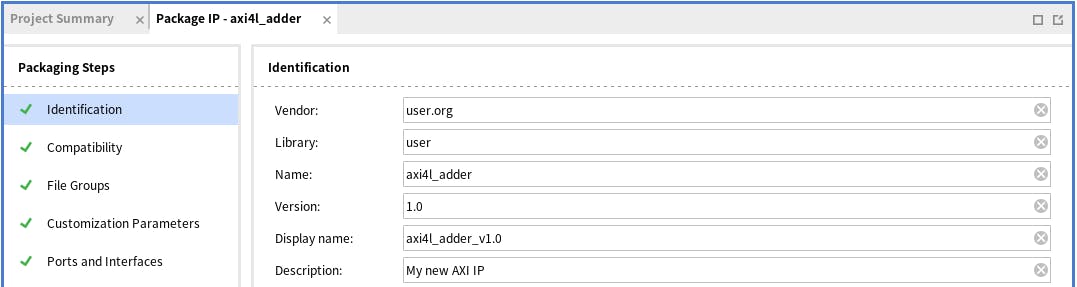

2) 在以下屏幕上,为 IP 命名。在这个演示中,我将展示一个简单的加法器,所以我的 IP 名称是axi4l_adder 。请注意底部字段中的目录位置,我们将很快导航到那里:

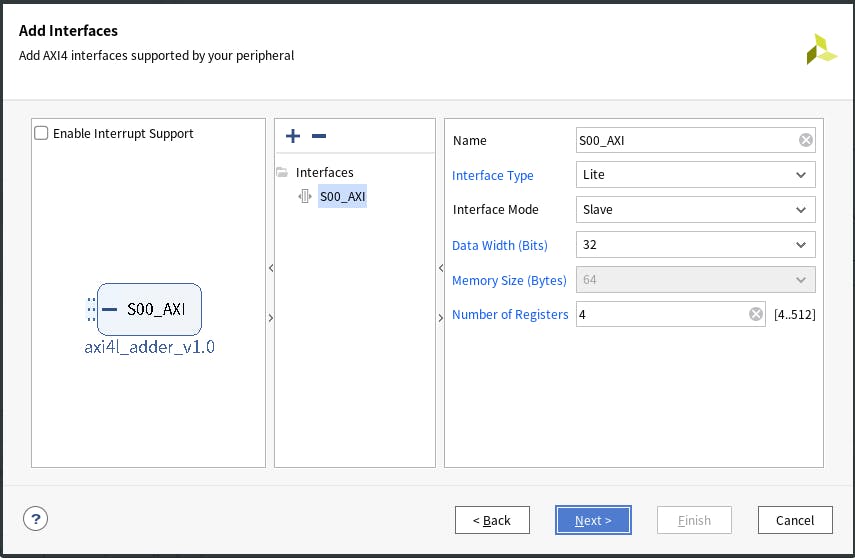

3)点击下一步,出现如下页面:

此演示的默认设置很好。它们将在 PL 中生成四个 32 位寄存器。4*32 = 128 位,因此 PS 将能够在此 PL 模块中寻址 16 字节的内存映射寄存器空间。

4) 单击下一步并滚动到“下一步”部分。选择“编辑 IP”,然后单击完成。将打开一个新的 Vivado 项目。

3. Vivado - IP 编辑器项目

3A。Verilog 加法器

1) 我们将在这个新的 Vivado 项目中编辑axi4l_adder IP。默认窗格应包含所有先前的信息:

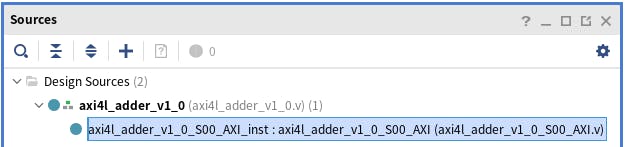

并且 Design Sources 窗格应该包含一些自动生成的 Verilog:

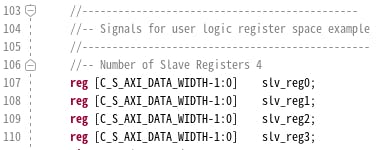

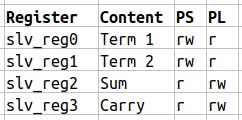

2) 双击axi4l_adder_v1_0_S00_AXI.v ,Vivado 将打开一个包含 HDL 源代码的新选项卡。模块 I/O 具有 AXI4-Lite 从接口的所有信号;不要碰。四个预期的寄存器位于 I/O 区域下方:

让我们定义加法器的预期行为:

- slv_reg0 : 附加项 1,由 PS 编写

- slv_reg1 : 加法项 2,由 PS 编写

- slv_reg2 : 项 1 和 2 的总和,由 PL 计算

- slv_reg3 : 加法进位,由 PL 计算

所以我们定义他们的权限:

回到 Verilog 文件中,在 reg 声明下方,有自动生成的进程有助于 AXI 信号发送以及寄存器写入/读取管理。我们需要做几件事:(1) 防止 PS 写入 slv_reg2 和 slv_reg3,(2) 计算和并进位 PL,(3) 将它们写入 slv_reg2 和 slv_reg3。

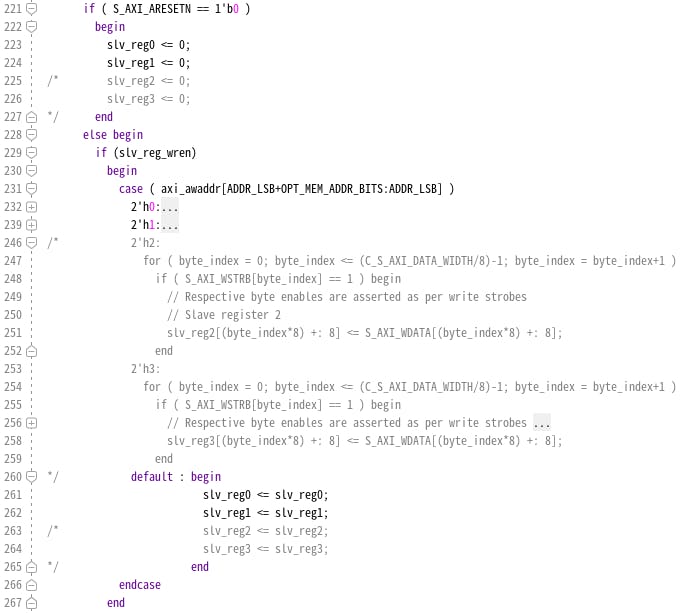

3) 为了防止 PS 写入禁止的寄存器,我们必须更新管理内存映射寄存器写入的专用进程。在第 210 行附近搜索注释“// 实现内存映射寄存器选择和写入逻辑生成” 。注释掉 slv_reg2 和 slv_reg3 分配,或完全删除它们:

现在 PL 可以改为管理这些寄存器。

4) 返回到第 115 行左右。提供一种称为sum的加法 reg 类型。它的大小将比slv_reg*信号大一位,以容纳进位位。

reg [C_S_AXI_DATA_WIDTH-0:0] sum;

5) 现在,导航到文件底部(“ //在此处添加用户逻辑”)。创建一个计算 reg0 和 reg1 之和的进程,然后写入slv_reg2&3。

// Add user logic here

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

sum <= 0;

slv_reg2 <= 0;

slv_reg3 <= 0;

end

else begin

sum <= slv_reg0 + slv_reg1;

slv_reg2 <= sum[$high(sum)-1:0]; // lower 32 bits

slv_reg3[0] <= sum[$high(sum)]; // top carry bit

end

end

// User logic ends

粘贴此代码后按 Ctrl+E。在源文件属性窗格中,将类型:Verilog 更改为类型:SystemVerilog。这对于使用诸如 $high() 之类的系统调用是必要的。

保存文件,让我们把 IP 包起来。

3B。打包IP

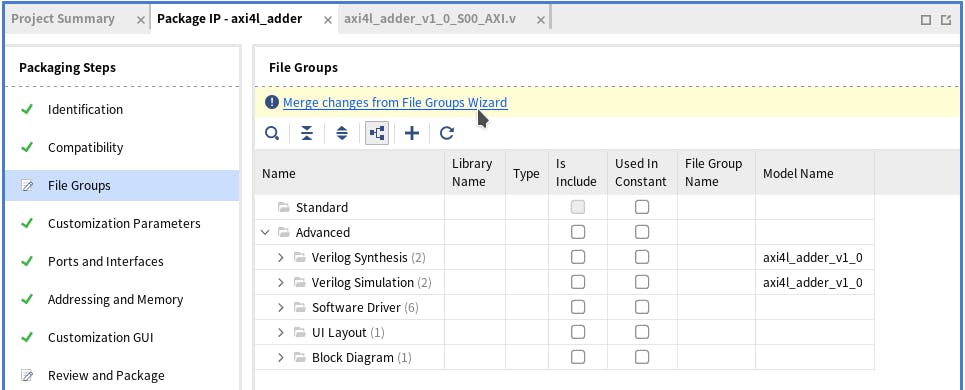

1) 返回“包 IP”选项卡。自从我们修改了 Verilog 源后,复选标记已从“文件组”部分中删除。点击“合并更改”:

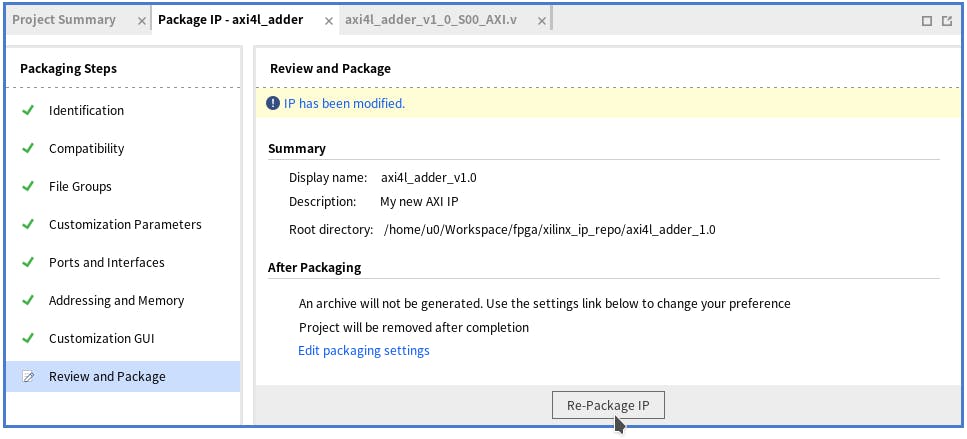

2) 现在在“Review”部分下,点击“Re-package”:

3)现在应该出现一个弹出窗口;关闭 IP 项目并返回 SoC 项目。

4. Vivado - SoC 项目实施

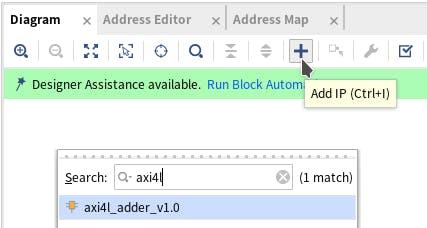

1) 回到 SoC 项目,我们可以使用新的 adder IP:

搜索 axi4l_adder,双击搜索结果,然后点击“运行连接自动化”的绿色横幅文本并使用默认设置。此步骤通过 AXI 互连模块从 Zynq M_AXI_GP0 连接到加法器 IP。

然后单击“运行块自动化”并使用默认设置。这一步对于在软件开发过程中使用 Zynq 的 UART1 接口是必要的。

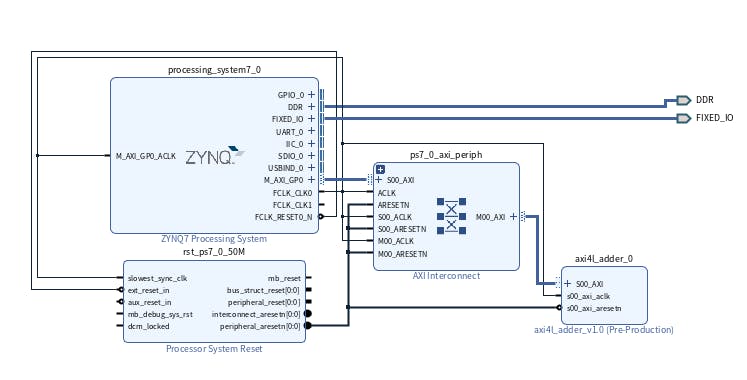

2) 模块设计应填充 AXI 互连和复位管理器:

PS 的 M_AXI_GP0 应连接到 AXI 互连,互连的 M00_AXI 应连接到 AXI4L 加法器 IP。如果您在 PS 块上看不到 M_AXI_GP0,则需要双击该块并在“AXI Non Secure Enablement”下拉列表下的 PS-PL 配置选项卡上选择“M AXI GP0 接口”。

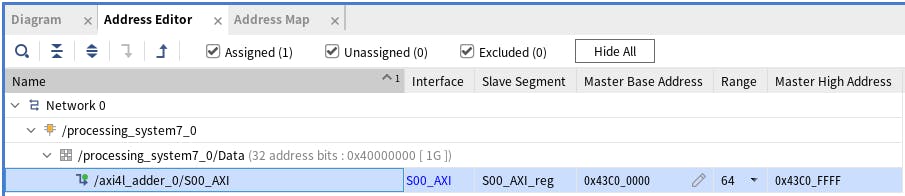

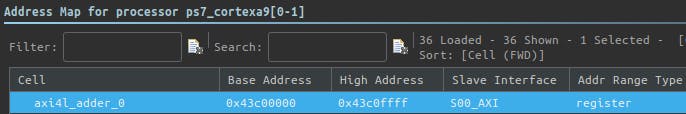

3) 在地址编辑器选项卡(“窗口”->“地址编辑器”)中,您应该看到列出的加法器 IP:

4) 按 F6 键验证模块设计。

5) 在 Sources 窗格中的 Design Sources 下,右键单击 .bd 文件并选择“Create HDL wrapper”->“Let Vivado manage and auto-update”。

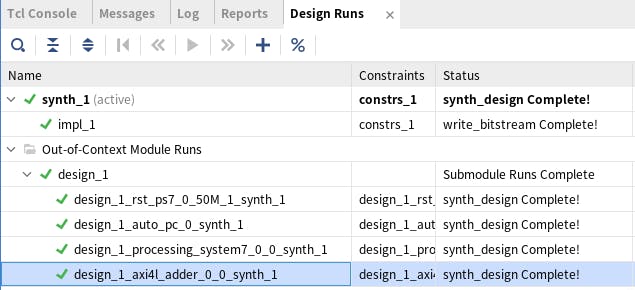

6) 点击“Generate Bitstream”按钮(或“Flow”->“Generate Bitstream”)让综合和实现运行。因为这是一个简单的 PS 项目,所以不需要 Vivado 约束。在设计运行下,您将看到 OOC 运行下的加法器 IP:

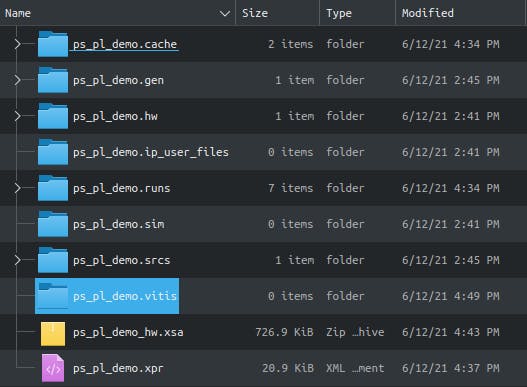

7) 一旦比特流生成完成,关闭弹出窗口并导航到“文件”->“导出”->“导出硬件”。在欢迎屏幕上点击下一步。在以下屏幕上,选择“包括比特流”。为硬件规范命名,并将其保存在 SoC 项目目录中。输出是在下面的 Vitis 中使用的 XSA 文件。

5. Vitis - 应用项目

5A。最初设定

1) [可选] 创建一个 Vitis 工作区文件夹(例如,在 SoC 项目文件夹中)。

2) 在 Vivado 中,点击“工具”->“启动 Vitis IDE”

3) Vitis 可以加载到欢迎屏幕,也可以在之前的工作区中开始。如果它从前一个工作区开始,点击“文件”->“切换工作区”并指向新目录[也是可选的]。

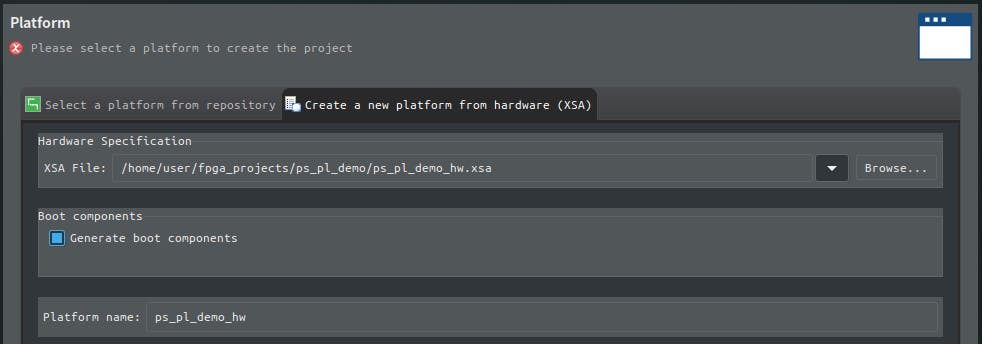

4) 单击创建应用程序项目(“文件”->“新建”->“应用程序项目”)。在欢迎页面点击下一步。

5) 在平台页面上,单击“从硬件创建新平台 (XSA)”选项卡。现在浏览以选择从 Vivado 导出的 XSA 文件。

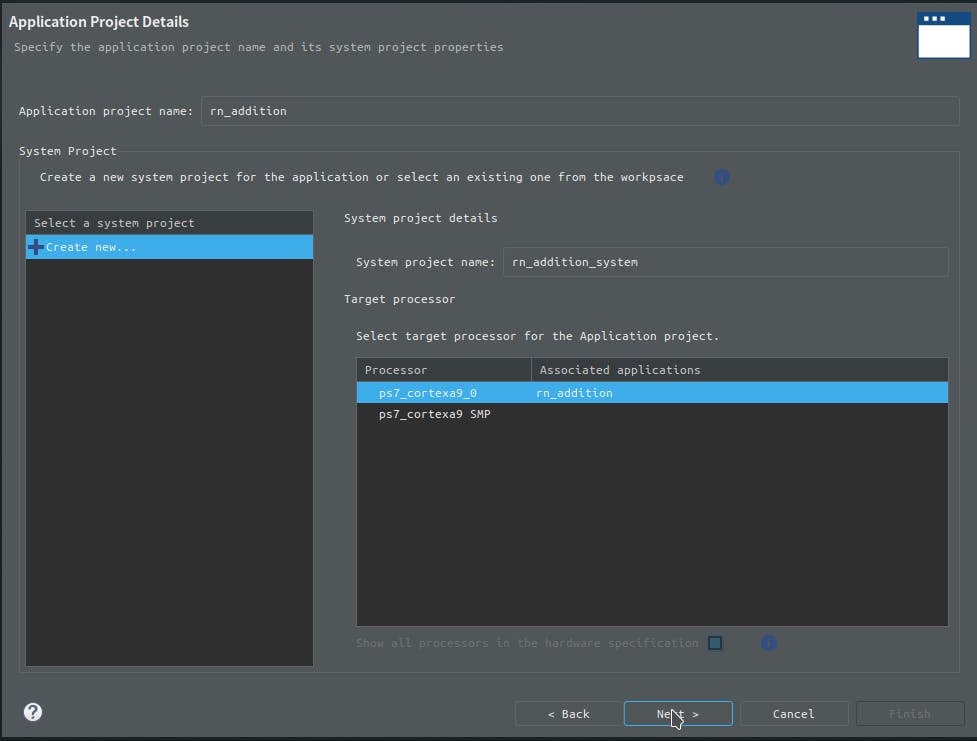

6)我们将添加一些随机数。创建一个名为rn_addition的新应用程序项目,然后单击 Next。

7)在下一页“域”上,默认设置就可以了。

8) 在“模板”页面上,选择 Hello World 模板并点击完成。

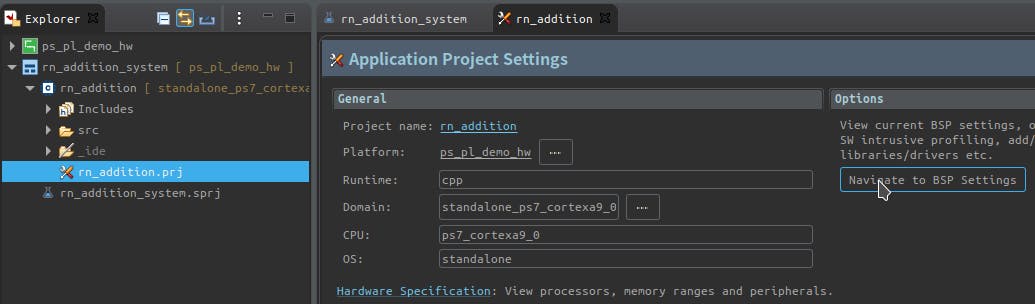

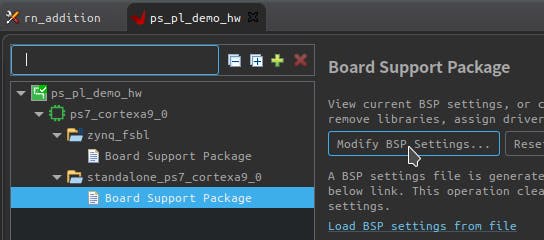

9) 现在在 Vitis 资源管理器中,选择 Application Project settings entry (rn_addition.prj) 并单击“Navigate to BSP settings”,

10) 现在点击“修改 BSP 设置”:

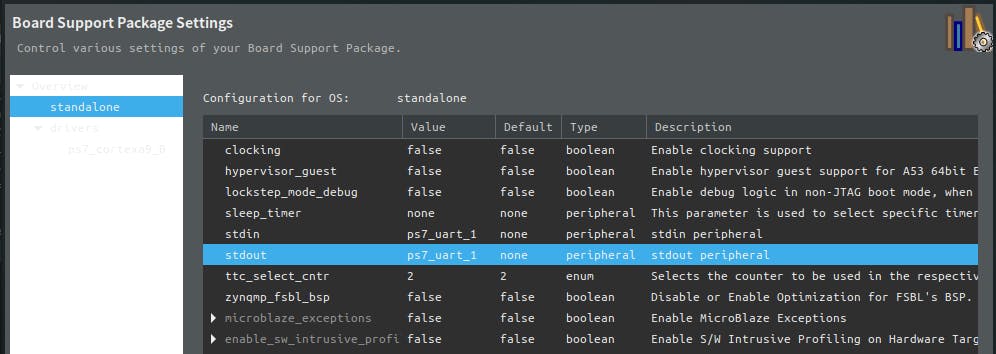

11) 在“Standalone”选项卡下,将 stdout 设置为 ps7_uart1。这可以使用 Zynq 的 UART 进行软件打印。单击确定并返回到应用程序项目设置选项卡。

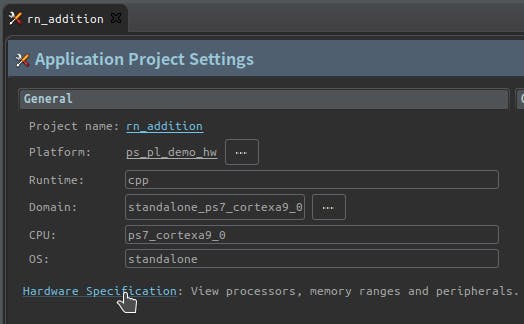

12) 在应用程序项目设置选项卡上,单击硬件规格:

13) 在结果选项卡中,AXI4L 加法器应位于地址映射中:

5B。创建随机数加法应用程序

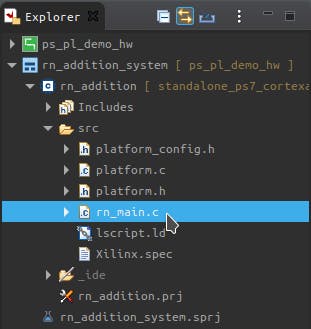

1) 现在我们可以做一些有用的事情了。在 Vitis 资源管理器窗格中,展开src 。将helloworld.c重命名为rn_main.c并双击进行编辑。

将 helloworld 代码替换为以下内容:

// J. Abate '21

#include // for random number function

#include // for sleep function

#include "platform.h"

#include "xil_printf.h"

#include "xil_io.h"

#define ADDER_b 0x43C00000

#define REG_0_o 0x0

#define REG_1_o 0x4

#define REG_2_o 0x8

#define REG_3_o 0xC

int main()

{

init_platform();

print("\nps7_uart_1 @ 115200 baud\n\n\r");

// random numbers; bottom and top of range

u32 rn_lo = 0x40000000, rn_hi = 0xBFFFFFFF;

// register data

u16 test_count = 1;

u32 slv_reg0_wdata = 0xFFFFFFFF;

u32 slv_reg0_rdata;

u32 slv_reg1_wdata = 0x1;

u32 slv_reg1_rdata;

u32 slv_reg2_rdata;

u8 slv_reg3_rdata;

while(1)

{

xil_printf("test #%d\n\r", test_count);

// Write then read slv_reg0

Xil_Out32(ADDER_b + REG_0_o, slv_reg0_wdata);

slv_reg0_rdata = Xil_In32(ADDER_b + REG_0_o);

xil_printf("slv_reg0 [w]|[r] = 0x%08X | 0x%08X (%u) \n\r", slv_reg0_wdata, slv_reg0_rdata, slv_reg0_rdata);

// Write then read slv_reg1

Xil_Out32(ADDER_b + REG_1_o, slv_reg1_wdata);

slv_reg1_rdata = Xil_In32(ADDER_b + REG_1_o);

xil_printf("slv_reg1 [w]|[r] = 0x%08X | 0x%08X (%u) \n\r", slv_reg1_wdata, slv_reg1_rdata, slv_reg1_rdata);

// Read slv_reg2&3

slv_reg2_rdata = Xil_In32(ADDER_b + REG_2_o);

slv_reg3_rdata = Xil_In8(ADDER_b + REG_3_o);

xil_printf("sum [r] | c [r] = 0x%08X | 0x%01X (%u) \n\n\r", slv_reg2_rdata, slv_reg3_rdata, slv_reg2_rdata);

// update terms for next iteration and increment the test count

slv_reg0_wdata = ( rand() % (rn_hi - rn_lo + 1) ) + rn_lo;

slv_reg1_wdata = ( rand() % (rn_hi - rn_lo + 1) ) + rn_lo;

test_count += 1;

sleep(10);

}

cleanup_platform();

return 0;

}

2)代码解释。我包括以下文件:

- rand() 函数的 stdlib.h

- unistd.h 用于 sleep() 函数

- xil_io.h用于内存映射寄存器 R/W 函数 Xil_In() 和 Xil_Out()

然后我定义要使用的内存地址。Vivado 地址编辑器和 Vitis 地址映射在基址 0x43C00000(偏移量 0x0 到 0xFFFF)处为加法器 IP 保留 64KB 地址。

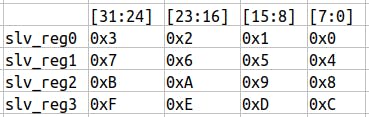

但是,请记住,加法器 IP 只有四个 32 位寄存器,总共 16 个字节(0x0 到 0xF):

- slv_reg0(偏移量 0x0 到 0x3):在此处写入第一个加法项

- slv_reg1(偏移量 0x4 到 0x7):在此处写入第二个加法项

- slv_reg2(偏移量 0x8 到 0xB):在此处读取总和

- slv_reg3 (offsets 0xC to 0xF): 在这里读取进位位

在 while(1) 循环中,Xil_Out() 和 Xil_In() 语句管理每个寄存器的写入/读取。

5C。运行应用程序

1) 返回 Vitis 资源管理器窗格,折叠所有展开的条目。突出显示平台项目和应用程序项目,然后右键单击并点击“构建项目”。构建完成后,点击 Bug 按钮旁边的下拉菜单,然后单击 Debug Configurations。

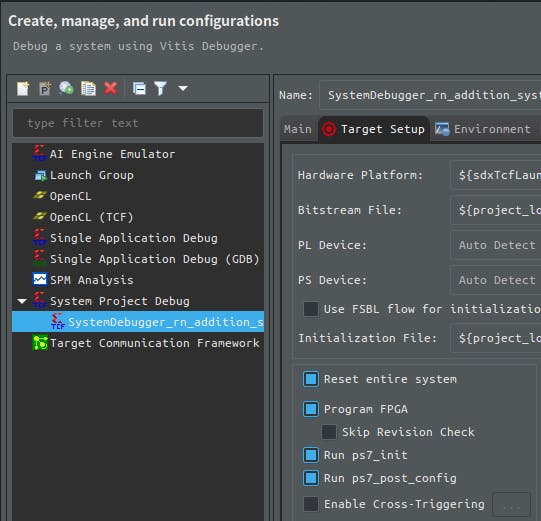

2) 在出现的弹出窗口中,双击“System Project Debug”并移动到 Target Setup 选项卡。确保选择“Program FPGA”,然后点击 Debug 关闭弹出窗口。

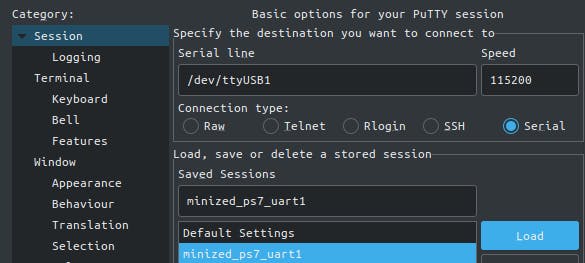

3) 现在,将 USB 电缆从计算机连接到 MiniZed 的 USB/JTAG/UART 端口。以 115200 波特率打开与 MiniZed UART 的串行会话:

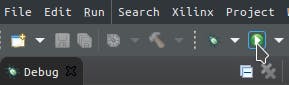

4) 回到 Vitis,点击运行按钮:

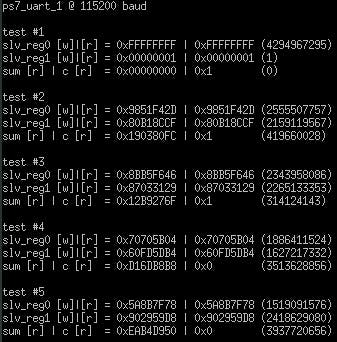

5) 在串行会话中,您应该会看到类似这样的打印:

每个测试显示以下内容:

- 测试ID#

- 写入 slv_reg0 和 slv_reg1 的项,在每个等号的右侧

- 从 slv_reg0 和 slv_reg1 读取的术语位于每个管道符号的右侧(括号中为无符号)。

- 从 slv_reg2 和 slv_reg3 读回的总和和进位结果(括号中的无符号总和)。

第一个测试是硬编码的,以显示从进位寄存器成功读取。随后的测试是伪随机的。

六、分析与结论

此演示展示了使用 PS 中的 Xil_In() 和 Xil_Out() 通过 AXI4-Lite 接口传输 PS-PL 数据。每当 PS 发出 Xil_Out() 以在 slv_reg0 或 slv_reg1 写入新项时,PL总是更新 slv_reg0 和 slv_reg1 项的总和。

在 PS 写入任一项之后的第一个时钟周期,PL 计算新的总和。在第二个时钟周期,它用和结果更新 slv_reg3,用进位结果更新 slv_reg4。与 Xil_Out32() 到 slv_reg1 和 slv_reg2 的 Xil_In32() 之间经过的时间相比,该延迟很小(两个 FCLK_0 周期 = 40 ns)。从这个意义上说,此演示假定 PL 在 PS 读取 slv_reg2 和 slv_reg3 时始终具有有效结果。

- ZMID4200 寄存器映射

- ZMID4200 寄存器映射

- STM32-寄存器地址名称映射分析

- STM32F103系列芯片的地址和寄存器映射原理、LED轮流闪烁实现

- STM32F103系列芯片的地址映射和寄存器映射原理,GPIO端口的初始化

- UG-1168:AD9544寄存器映射参考手册

- UG-1167:AD9543寄存器映射参考手册

- UG-1146:AD9545寄存器映射参考手册

- 寄存器的名称和地址的映射详细资料分析

- 如何进行寄存器名称和地址的映射分析

- HELLODSP中F2812寄存器速查 12次下载

- 多寄存器Load/Store内存访问指令 1次下载

- 移位寄存器及其应用实验 22次下载

- 寄存器与移位寄存器

- 集成移位寄存器

- 寄存器和内存的区别 935次阅读

- ARM通用寄存器及状态寄存器详解 6337次阅读

- CPU、寄存器和内存单元的物理结构 3962次阅读

- FPGAs,Zynq和Zynq MPSoC器件的特点 2275次阅读

- ZYNQ7020的PS端的基本开发流程 7018次阅读

- 寄存器与内存的区别 9939次阅读

- 计算机中内存、cache和寄存器之间的关系 4874次阅读

- 寄存器变量 2243次阅读

- 寄存器比内存快的原理是什么? 5212次阅读

- Linux驱动开发笔记:对zynq PL部分IP核的驱动开发过程 9483次阅读

- zynq中PL部分的物理地址操作函数 6815次阅读

- 逆向基础之寄存器和内存详解 2902次阅读

- 为什么寄存器比内存快_原因是这个 6874次阅读

- Zynq PS/ PL第五篇:Adam Taylor MicroZed系列之25 539次阅读

- Zynq PS / PL 第四篇:Adam Taylor MicroZed系列之 24 1056次阅读

下载排行

本周

- 1山景DSP芯片AP8248A2数据手册

- 1.06 MB | 532次下载 | 免费

- 2RK3399完整板原理图(支持平板,盒子VR)

- 3.28 MB | 339次下载 | 免费

- 3TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 4DFM软件使用教程

- 0.84 MB | 295次下载 | 免费

- 5元宇宙深度解析—未来的未来-风口还是泡沫

- 6.40 MB | 227次下载 | 免费

- 6迪文DGUS开发指南

- 31.67 MB | 194次下载 | 免费

- 7元宇宙底层硬件系列报告

- 13.42 MB | 182次下载 | 免费

- 8FP5207XR-G1中文应用手册

- 1.09 MB | 178次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537798次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191187次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

德赢Vwin官网

App

德赢Vwin官网

App

发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论