完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > VHDL语言

VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述语言)。VHSIC是Very High Speed Integrated Circuit的缩写,是20世纪80年代在美国国防部的资助下始创的,并最终导致了VHDL语言的出现。

VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述语言)。VHSIC是Very High Speed Integrated Circuit的缩写,是20世纪80年代在美国国防部的资助下始创的,并最终导致了VHDL语言的出现。1987 年底,VHDL被 IEEE 和美国国防部确认为标准硬件描述语言。VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述语言)。VHSIC是Very High Speed Integrated Circuit的缩写,是20世纪80年代在美国国防部的资助下始创的,并最终导致了VHDL语言的出现。1987 年底,VHDL被 IEEE 和美国国防部确认为标准硬件描述语言。VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

VHDL 语言能够成为标准化的硬件描述语言并获得广泛应用,它自身必然具有很多其他硬件描述语言所不具备的优点。归纳起来,VHDL 语言主要具有以下优点:

(1) VHDL 语言功能强大,设计方式多样

VHDL 语言具有强大的语言结构,只需采用简单明确的VHDL语言程序就可以描述十分复杂的硬件电路。同时,它还具有多层次的电路设计描述功能。此外,VHDL 语言能够同时支持同步电路、异步电路和随机电路的设计实现,这是其他硬件描述语言所不能比拟的。VHDL 语言设计方法灵活多样,既支持自顶向下的设计方式,也支持自底向上的设计方法; 既支持模块化设计方法,也支持层次化设计方法。

(2) VHDL 语言具有强大的硬件描述能力

VHDL 语言具有多层次的电路设计描述功能,既可描述系统级电路,也可以描述门级电路;描述方式既可以采用行为描述、寄存器传输描述或者结构描述,也可以采用三者的混合描述方式。同时,VHDL 语言也支持惯性延迟和传输延迟,这样可以准确地建立硬件电路的模型。VHDL 语言的强大描述能力还体现在它具有丰富的数据类型。VHDL 语言既支持标准定义的数据类型,也支持用户定义的数据类型,这样便会给硬件描述带来较大的自由度。

(3) VHDL 语言具有很强的移植能力

VHDL 语言很强的移植能力主要体现在: 对于同一个硬件电路的 VHDL 语言描述,它可以从一个模拟器移植到另一个模拟器上、从一个综合器移植到另一个综合器上或者从一个工作平台移植到另一个工作平台上去执行。

(4) VHDL 语言的设计描述与器件无关

采用 VHDL 语言描述硬件电路时,设计人员并不需要首先考虑选择进行设计的器件。这样做的好处是可以使设计人员集中精力进行电路设计的优化,而不需要考虑其他的问题。当硬件电路的设计描述完成以后,VHDL 语言允许采用多种不同的器件结构来实现。

(5) VHDL 语言程序易于共享和复用

VHDL 语言采用基于库 ( library) 的设计方法。在设计过程中,设计人员可以建立各种可再次利用的模块,一个大规模的硬件电路的设计不可能从门级电路开始一步步地进行设计,而是一些模块的累加。这些模块可以预先设计或者使用以前设计中的存档模块,将这些模块存放在库中,就可以在以后的设计中进行复用。

由于 VHDL 语言是一种描述、模拟、综合、优化和布线的标准硬件描述语言,因此它可以使设计成果在设计人员之间方便地进行交流和共享,从而减小硬件电路设计的工作量,缩短开发周期。

模型机控制信号产生逻辑VHDL 引言: 随着科技的发展,数字系统的设计越来越重要。在数字系统设计的过程中,模型机控制信号的产生逻辑是一个非常重要的方面。...

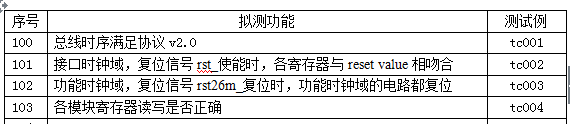

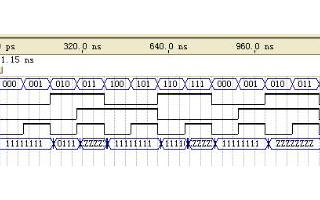

Timer测试方案 Timer测试平台实现 测试平台debug注意事项

IC验证,一般也称“功能验证”,我们今天要讲的,不是这个,是它的简化版:模块测试,是设计工程师完成代码设计后,需要自己做的这部分验证工作。IC验证,我们...

一个完整的VHDL程序包括实体(Entity),结构体(Architecture),配置(Configuration),包集合(Package),库(L...

2022-11-09 标签:VHDL语言 4938 0

什么是vhdl语言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述语言)。VHSIC是...

2020-04-23 标签:VHDL语言 1.2万 0

VHDL是一种用来描述数字逻辑系统的“编程语言”。它通过对硬件行为的直接描述来实现对硬件的物理实现,代表了当今硬件设计的发展方向。VHDL是为了满足逻辑...

2020-04-23 标签:VHDL语言 2911 0

在VHDL程序中,实体(ENTITY)和结构体(ARCHITECTURE)这两个基本结构是必须的,他们可以构成最简单的VHDL程序。通常,最简单的VHD...

2020-04-23 标签:VHDL语言 4654 0

--TLC5510 VHDL 控制程序 --文件名:TLC5510.vhd --功能:基于VHDL语言,实现对高速A/D器件TLC5510控制 --最后...

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |