完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

德赢Vwin官网 网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

智能科技已经无缝融入到每个人的生活中。使用智能音箱查询天气、播放歌曲、甚至进行会议提醒确实很方便,但如果黑客能够访问你所有的数据和交易信息,那会不会是一场灾难呢?在万物智能(Pervasive Intelligence)时代,人工智能(AI)和安全已经成为超越传统芯片设计界限的关键因素。 半导体行业...

当前的电源设计正越来越多地转向更高级别的架构,包括高效拓扑和数字电源。因此,工程师们现在希望通过人工智能进行更大量的数字仿真,以推动日益复杂的设计以及电源和射频工作。...

DFT Design For Test,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT的常见方法就是,在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元。...

十多年来,EDA高层管理人员一直在寻求扩展到相邻市场的机会但无果。实际上,直到2016年西门子以45亿美元收购Mentor Graphics之前,该领域唯一重要的一步是朝相反的方向迈出的。自那时以来,有三件事发生了根本性的变化。...

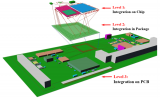

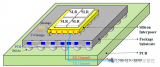

封装内集成的基本单元是上一步完成的裸芯片或者小芯片Chiplet,我们称之为功能单元 (Function Unit),这些功能单元在封装内集成形成了SiP。...

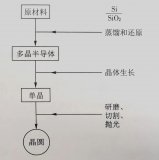

从液态的熔融硅中生长单晶硅的及基本技术称为直拉法(Czochralski)。半导体工业中超过90%的单晶硅都是采用这种方法制备的。...

在当前高速设计中,主流的还是PAM4的设计,包括当前的56G,112G以及接下来的224G依然还是这样。突破摩尔定律2.5D和3D芯片的设计又给高密度高速率芯片设计带来了空间。...

EDA,是指电子设计自劢化( Electronic Design Automation)用于芯片设计时的重要工具,设计时工程师会用程式码规划芯片功能,再透过EDA 工具让程式码转换成实际的电路设计图。...

制程技术决定了芯片上晶体管的尺寸和密度。较小的晶体管尺寸意味着更高的集成度,可以提供更高的性能和更低的功耗。...

先进封装中架构的丰富性和失败的高成本鼓励器件设计流程和封装厂之间更密切的合作。EDA 公司和 OSAT 正在开发协作设计工具集,以提高封装性能、降低成本并缩短集成封装的上市时间。...

纳米片晶体管并不能拯救摩尔定律,也不能解决代工厂在最先进工艺节点上面临的所有挑战。为了克服这些问题,代工厂正在寻求各种创新,例如背面供电(BSPD),以在节省功耗的同时从晶体管之间的互联中获得更多性能。...

机遇总是与挑战并存,目前国内在高端EDA工具研发方面,面临着如Synopsys、Cadence和Mentor等国际EDA供应商的巨大挑战,即使是作为本土最大的EDA公司,华大九天目前也只能够提供产业所需EDA解决方案的1/3左右。...

SOC ( System on Chip)是在同一块芯片中集成了CPU、各种存储器、总线系统、专用模块以及多种l/O接口的系统级超大规模集成电路。 由于SOC芯片的规模比较大、内部模块的类型以及来源多样,因此SOC芯片的DFT面临着诸多问题。...

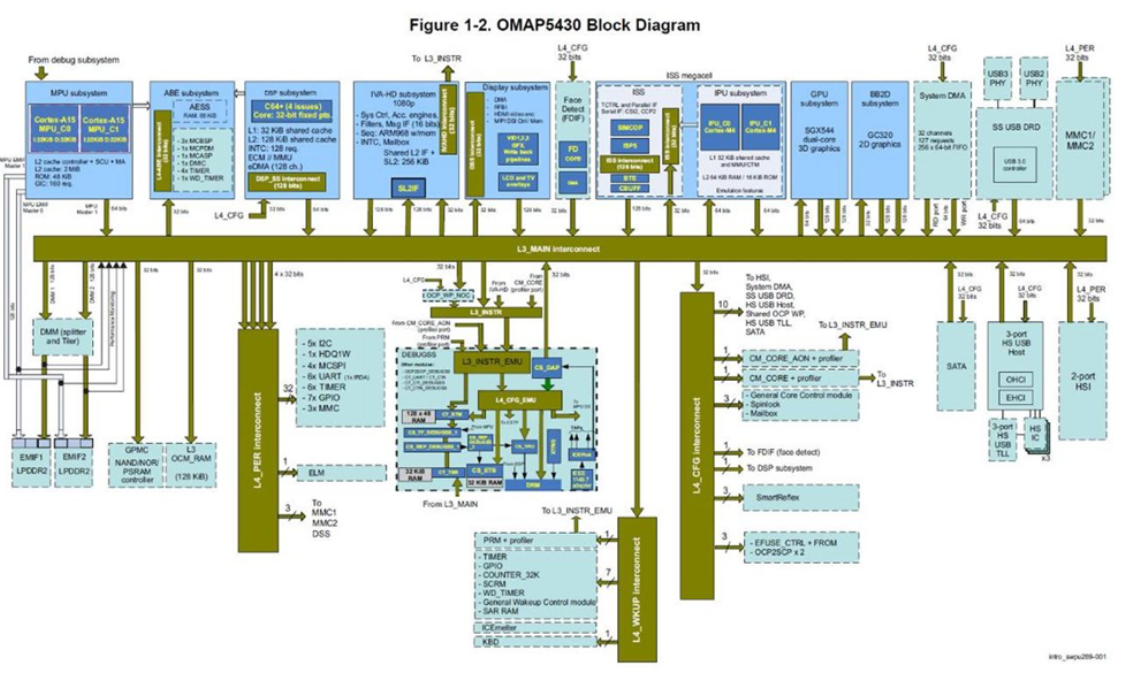

考虑当今使用的层次结构形式的最简单方法是要求工程师从概念上设计一个系统。他们可能会开始绘制一个包含大块的框图,其中包含 CPU、编码器、显示子系统等标签。这不是一个功能层次结构,尽管许多划分的块被认为是提供功能的。这也不是纯粹的结构分解,因为在芯片中,一切都变成了晶体管的无定形海洋。...

DIP是很多中小规模集成电路喜欢采用的封装形式,其引脚数一般不超过100个。采用DIP封装的CPU芯片有两排引脚,在使用时,需要插入到具有DIP结构的芯片插座上,也可以直接插在电路板上进行焊接,如传统的8051单片机很多采用这种封装形式。...

芯天成版图集成工具EsseDBScope,是基于国微芯EDA统一数据底座研发的标志性工具,本次推出的更新版本,新增了IP merge、LVL、Signal tracing、PG Find short等功能。...