用EPLD实现的单脉冲二次雷达应答处理器。其主要功能包括:应答框架脉冲检测,应答信息解码,将应答信息装配成飞机的同步应答组形成目标报告,丢弃非同步虚假应答。

1 一次雷达与二次雷达

二次雷达与一次雷达基本上是并行发展的。与一次雷达相比,二次雷达有回波强、无目标闪烁效应、询问波长与应答波长不等的特点,从而消除了地物杂波和气象杂波的干扰。单脉冲技术应用于二次雷达,可以方便地基于多个波束对目标测量,进而有效地增加数据冗余度,提高角度测量的精度。对应答处理而言,单脉冲技术的应用,大大提高了在混叠或交织情况下对应答码的解码能力,使单脉冲二次雷达与常规二次雷达相比实现了一次质的飞跃。

二次雷达与一次雷达的根本区别是工作方式不同。一次雷达依靠目标对雷达发射的电磁波的反射机理工作,它可以主动发现目标并对目标定位;二次雷达则是在地面站和目标应答机的合作下,采用问答模式工作。目前的航管二次雷达共有七种询问模式,分别称为1、2、3/A、B、C、D和S模式。根据询问脉冲P1与P3 的间距决定(S模式除外)各种询问模式。

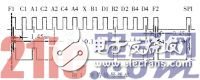

机载应答机发出的应答码由16个信息码位组成,这些码位的代号依次是 F1、C1、A1、C2、A2、C4、A4、X、B1、D1、B2、D2、B4、D4、F2 和SPI。每个码位都有两种状态,即有脉冲或无脉冲。有脉冲时为“1”,无脉冲时为“0”。F1与F2的0.5电平处的脉冲前沿间隔为 20.3±0.1μs,称为框架脉冲,它们是二次雷达应答信号的标志脉冲,均恒为“1”状态。X位是备用状态,恒为“0”。两个框架脉冲(F1与F2)之间的12个信息码位,可以编成4 096个独立的应答码。SPI是特殊定位识别码,当两架飞机相互接近或者应答码相同时,调度员可以要求其中的一架飞机在已回答的12个码位基础上再增加一个SPI脉冲,以便准确识别。二次雷达应答信号组成如图1所示。

2 应答处理器系统组成

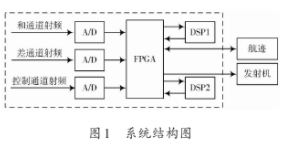

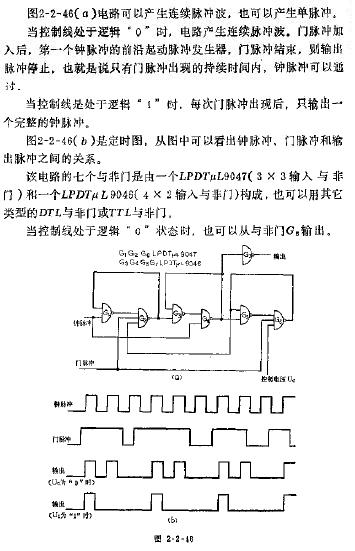

单脉冲二次雷达应答信号处理的基本流程如图2所示。

在视频预处理器中,和与差支路的∑、△视频信号,经A/D转换器进行数字化处理后,变成两组8位的数字信号传送给应答处理机;将∑接收单元与△接收单元的信号经相位鉴别器,生成表示目标在波束中心左侧或右侧的轴向指示信号BI(2位),送应答处理器;∑与Ω两视频幅度进行比较,产生表示应答为旁瓣应答还是主瓣应答的RSLS(1位);接收信号经6dB检测、反窄处理、二分层产生PSV(处理后的和视频,1位)。视频预处理器产生上述信号并输入给应答处理机,进行框架检测、和差比计算、码装配等处理,最终形成应答报告输出给点/航迹处理计算机。应答处理机系统的组成如图3。

在应答处理机中选用了Lattice公司的EPLD作为主处理芯片(ispLSI1032E)。该芯片有64个I/O端,8个指定输入端,6 000个逻辑门,192个寄存器,最大时延≤12ns,通过简单的5线接口,即可用PC机对线路板上菊花链结构的最多8个芯片进行编程。PC104是嵌入式计算机,其CPU是一片兼容的64位第六代处理器,运行速度可达300MHz,其图形处理器可支持各种LCD及TFT显示屏,同时支持PS/2键盘、 PS/2鼠标、两串行接口、一并行接口、USB接口、声卡功能。

应答处理机的工作原理:1位PSV、8位和视频、8位差视频、2位轴向指示及1位接收旁瓣抑制信号,在经过输入缓冲并与系统时钟信号同步后,其中的PSV 信号进入边沿产生电路,所产生的前沿延迟一个框架时间(20.3μs)后与未延迟的前沿信号相与给出目标框架,启动4个解码器中处于空闲状态的装配器开始解码工作,产生解码需要的定时脉冲序列。同时和视频、差视频、轴向指示、旁瓣抑制信号送入视频采样电路,经过视频采样产生的SVA(和视频幅度)和 DVA(差视频幅度)经和差比计算电路产生SDR值,SVA、DVA、SDR送数字寄存器进行延迟,延迟及未延迟的SVA、SDR、轴向指示、接收旁瓣抑制和目标前沿信号一起送入代码装配器,在定时脉冲的作用下,对目标应答信息进行解码、去除幻影应答、解旁瓣应答和军事告急应答。经过进一步相关、确认和修正后,将目标的SVA和SDR代码、综合的代码置信度信息及一些标志信息送代码装配总线,在输出控制的情况下依次写入先进先出(FIFO),PC机依次读出GPS时间信息及FIFO中的目标报告。

3 系统的具体实现

3.1 旁瓣抑制与边沿提取

近距离的飞机能够被天线的旁瓣探测到,但如果没有特殊的旁瓣抑制措施,就会使地面接收装置接收到来自旁瓣的应答信息,从而夸大飞机的数量。P2作为旁瓣抑制脉冲由Ω通道发射,在天线的主瓣波束内,P1与P3的幅度会高于P2,而在天线的旁瓣内,P2会高于P1与P3,机载应答机根据P1、P3与P2的幅度关系决定是否做出应答,对旁瓣内的询问不予应答。

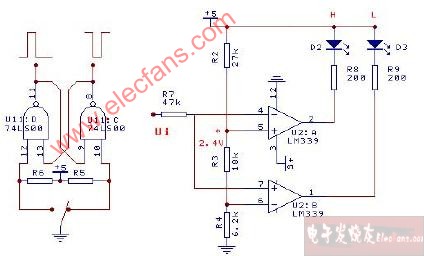

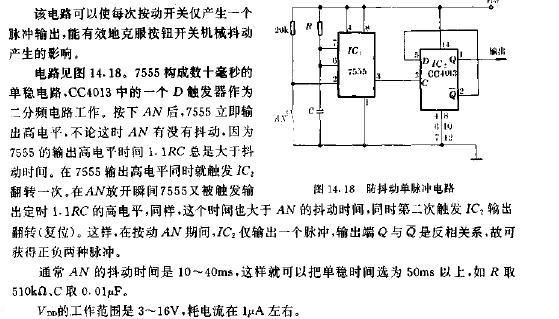

单脉冲二次雷达的PSV信号是由接收机和通道(∑)内的应答信号,经过特定门限电平进行二值化处理后输出的0或1电平。前后沿的提取,可以将PSV信号输入两个寄存器,通过与门电路实现。实现电路如图4所示。

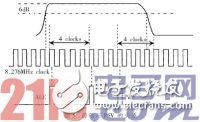

ALE与ATE分别是与时钟脉宽(0.1208μs)相同的前沿与后沿。当PSV信号的宽度大于一个应答码的宽度时,就认为接收到的是两个或多个脉冲的混叠,于是产生了一个伪前沿(PLE)。PLE的产生时间是从ATE开始向前数四个时钟周期(因为一个标准的脉冲宽度为四个时钟周期),如果PSV的脉宽更长,可认为有更多个应答脉冲的交叠,一个额外前沿(XLE)在ALE与PLE之间产生,在以后的处理中只用于帮助判断结果的正确性。前沿与PSV的关系如图5所示。

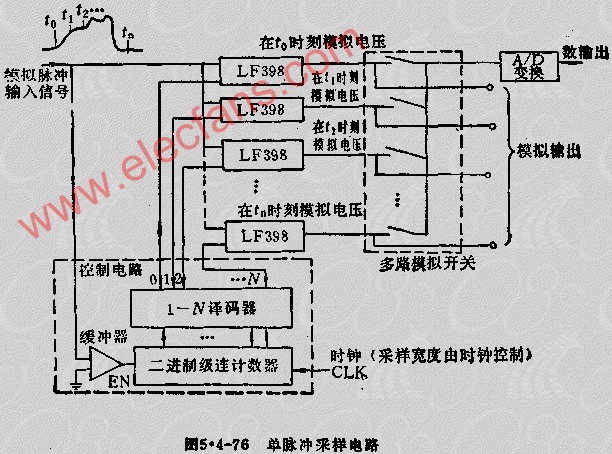

3.2 视频采样

视频采样分为ALE采样与PLE采样。

ALE采样使用了4×4寄存器阵列,这样就能够存储多于一个的采样值。为确保寄存器阵列的建立与保持时间,ALE脉冲经一级触发后,由延迟器产生一个 40μs的延迟,并限制写脉冲到30μs。寄存器阵列的写地址由4位计数器产生,每个采样脉冲计数器加1。PLE采样与ALE采样电路不同之处是它只需要存储一个PLE采样值。本系统的采样时钟为8.276MHz。

3.3 SDR计算

由于SDR模块中采用了对数运算,所以在进行和幅度与差幅度比值的运算时,只需要将差信号反相后接在加法器的输入端。除在波束中心外的和信号小于差信号外,△-∑在波束中心出现负峰值,所以在负峰值最大处为波束的中心。根据其他△-∑的值并参照负峰值,可转化为偏离波束中心的角度。

3.4 框架检测与应答解码

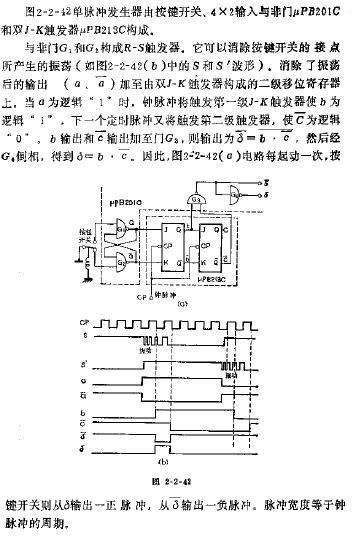

正常情况下,两个框架脉冲的间隔为20.3±0.1μs,因此,一个框架就认为两个前沿间有167、168或169个时钟周期。本系统框架脉冲的检测是根据比较延时的前沿与非延时情况下的重合情况,如图6所示。延时的前沿对应于框架脉冲F1,非延时的前沿对应脉冲F2,F1相对于F2延时20.3μs。由于F2相对于F1有3个时钟脉冲的变化范围,所以F2与F1的前沿延时167、168或169个时钟周期的任一个对齐,都认为是一个正确的框架。

以下三种情况下框架检测将被禁止:

(1)F1、F2都是来自旁瓣的应答信号;

(2)两个相邻的框架之间的间隔小于3个时钟周期;

(3)S模式的头应答被检测到,框架检测间被禁止120μs,因为一个S模式应答持续120μs。

应答信息相互交织产生幻影框架,如图7所示。假如只用框架脉冲间的时间间隔为20.3μs的原则检测,可检测到4个框架脉冲对,框架检测器不能区分“虚假”框架和来自飞机的真实框架脉冲对。

补救措施是同时只处理两个应答。当第一个应答被检测到,随后21μs中检测到的应答为临时应答,如果另外又发现一个重叠应答,这个临时应答就被取消此过程重复进行,直到检测到最后一个应答,此应答被保留。因为第一个检测到的框架肯定是真实应答,没有更早的脉冲产生错误框架。同样,最后一个框架肯定是真实应答,没有更晚的脉冲能产生错误框架,中间检测到的框架是可疑的,假定它们不正确。

当一个正确的框架被检测到,接下来的任务就是检测此次应答码的内容。首先,解码过程依据每个应答码间的时间间隔都是1.45μs,SPI与F2间的时间间隔是4.35μs,因此在离框架脉冲各个应答码可能出现的位置上检测是否有应答脉冲出现。考虑到每个应答码与框架脉冲间的时间间距有一定的允许误差,在距框架脉冲相应的应答码出现的位置上,提前或延后一个时钟周期都认为是正确应答码的位置。将相对于框架脉冲可能出现应答码的位置上的值与框架脉冲(非旁瓣脉冲)比较,得出应答码为1或0,有以下几种情况:

(1)高置信度0:在应答码出现的地方没有检测到应答脉冲的存在,若仅以幅度测量,则仅出现低幅度值。

(2)高置信度1:在应答码出现的地方出现主波束内的应答码,幅度与其对应的参考脉冲相关,与其他应答的参考脉冲不相关。

(3)低置信度0:若此应答脉冲被标记为旁瓣应答脉冲或此应答脉冲与相应的参考脉冲不相关,则与其他应答的参考脉冲相关。

(4)低置信度1:主波束应答码存在,但与参考脉冲不相关或与另外应答的参考脉冲相关,或既与相应的应答框架相关又与另外的框架相关。

3.5 码装配

码装配包括SVA代码装配器和SDR代码装配器两部分。SVA代码装配器的功能根据SVA平均值进行置信度确定,产生对应的置信度码位;SDR代码装配器的功能是检测到一个框架对 F1、F2时,便检查该应答脉冲的内容。对每个代码位,根据SDR 平均值进行置信度确定,产生对应的置信度码位,然后将该代码和置信度位与来自SVA装配器的相应位进行组合。

因为最多能同时处理四个应答,故有四组相同的SVA代码装配器和SDR代码装配器。其主要工作原理是:为了求得SVA的平均值,需要在一个应答的起始时刻建立一个SVA的参考值。一般情况下,以F1为参考值,若F1为旁瓣应答或反射应答,则用F2为参考值。当应答码与参考值相比,得到一个高置信度码时,产生的SVA值才被认为是一个应答码。SDR的工作过程与SVA类似。把SVA代码/置信度与相应的SDR代码/置信度进行组合,串行输出的代码和置信度码经过串-并转换输出到FIFO,计算机(PC104)读取FIFO的内容,送给点/航迹计算机处理,显示飞机的相关信息。

二次雷达在民航系统和军用敌我识别系统中起着非常重要的作用。随着飞机密度的增加,对二次雷达的性能提出了更高的要求。利用上述应答处理器,使单脉冲二次雷达达到≥400批/天线转的处理能力,同时提高了处理精度,减小了系统的体积,增加了灵活性。

德赢Vwin官网

App

德赢Vwin官网

App

评论