LMK6 时钟发生器 计时 评估板

2024-03-14 23:22:15

CS2200-CP 时钟发生器 时钟定时 mikroBUS™ Click™ 平台评估扩展板

2024-03-14 23:11:37

Si5348 时钟发生器 计时 评估板

2024-03-14 22:30:44

Si50122-A5 时钟发生器 计时 评估板

2024-03-14 22:30:31

ICS501 时钟发生器 时钟定时 mikroBUS™ Click™ 平台评估扩展板

2024-03-14 22:03:12

时钟 扇出缓冲器(分配) IC 1:5 20-SOIC(0.295",7.50mm 宽)

2024-03-14 21:23:26

Si5351A 时钟发生器 时钟定时 STEMMA QT 平台评估扩展板

2024-03-14 20:37:59

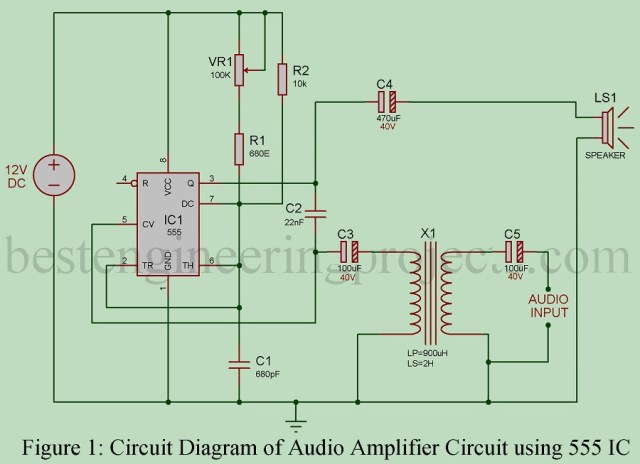

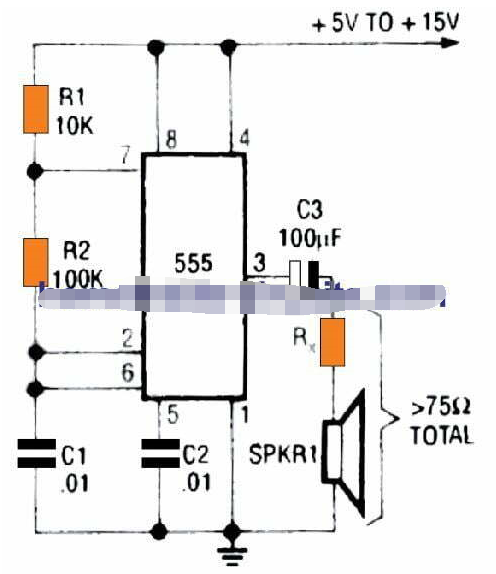

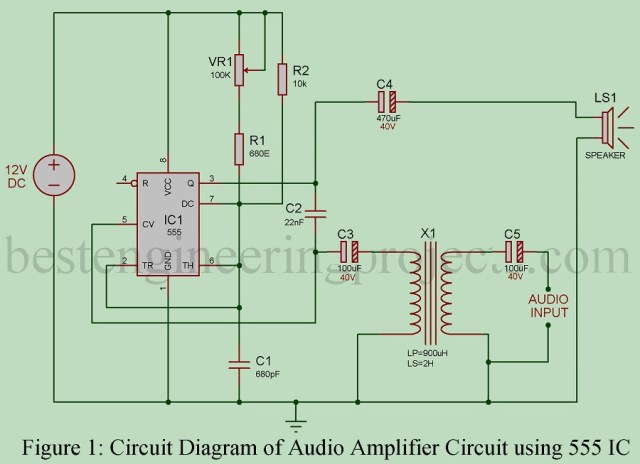

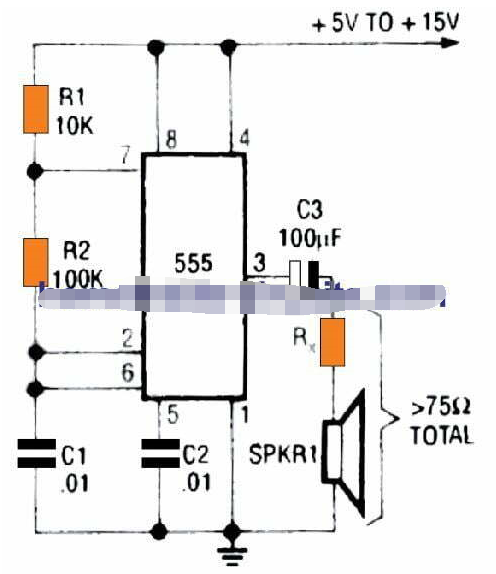

作为电子爱好者,我们都知道定时器 IC555。定时器 IC 555 因其应用而成为有史以来最受欢迎的 IC之一。该IC具有各种应用,如时钟脉冲发生器、延时电路等。

2024-02-25 16:43:18 187

187

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2024-02-04 11:41:14

IC放大器是一种集成电路,用于放大电信号。它通常由多个电子元器件集成在一块芯片上,可以实现特定的功能。

2024-02-01 16:32:30 163

163 德赢Vwin官网

网站提供《毫微微时钟网络同步器、抖动衰减器和时钟发生器RC32112A 数据表.pdf》资料免费下载

2024-01-31 10:09:17 0

0 波特率发生器是一种用于控制串行数据通信速率的设备,它可以生成特定波特率的时钟信号。在嵌入式系统、通信设备和计算机硬件中,波特率发生器的使用十分常见。波特率发生器通常使用定时器来实现时钟信号的生成

2024-01-24 09:56:20 265

265 集成电路(Integrated Circuit,简称IC)是指在一个芯片上集成了多个电子器件和电子元件的电路。这些电子器件和电子元件包括晶体管、电容器、电感器、二极管、三极管等等。通过提供不同的供电

2024-01-22 11:03:18 823

823 “核芯互联CLG440是一颗专为高性能服务器、计算中心应用推出的支持PCIe 6.0、符合CK440Q标准的高性能时钟发生器。

2024-01-16 15:57:40 279

279

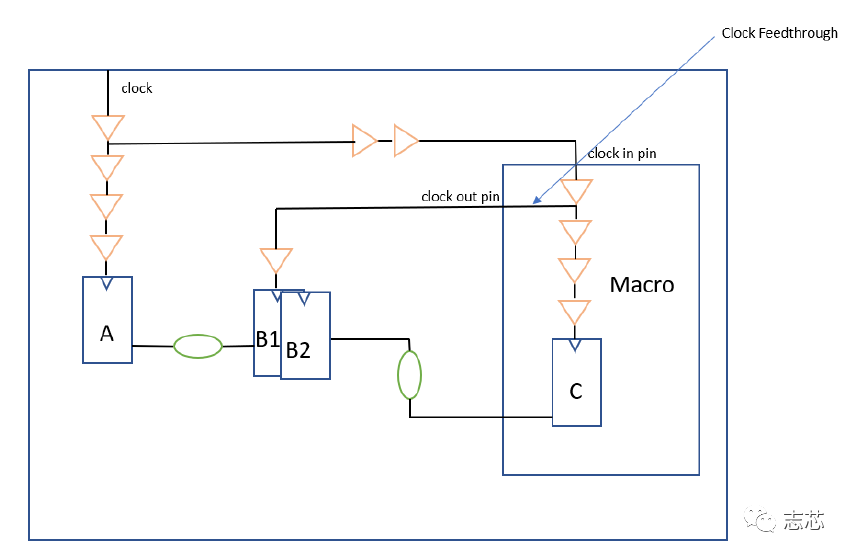

网络 时钟分配网络是实现异步电路的一种常用方法。它将一个主时钟信号分发给整个电路,以确保电路中的所有部件都按照相同的时钟进行操作。时钟分配网络通常包含许多时钟树,每个时钟树都将时钟信号传递给一部分电路。时钟分配网

2024-01-16 14:42:44 208

208 控制系统之间如何实现时钟同步? 控制系统之间的时钟同步是确保不同系统之间的时钟保持一致的过程。它在许多实时应用中非常重要,如分布式系统、通信网络、工业自动化等。时钟同步的目标是确保所有控制系统在各个

2024-01-16 14:37:23 188

188 方面的要求。所以在管脚分配前对 FPGA工作的环境要相当的熟悉,要对其中的信号来自哪里去向何方非常的清楚,这就按照连线最短的原则将对应的信号分配到与外部器件连线最近的 BANK 中。2、 掌握

2024-01-10 22:40:14

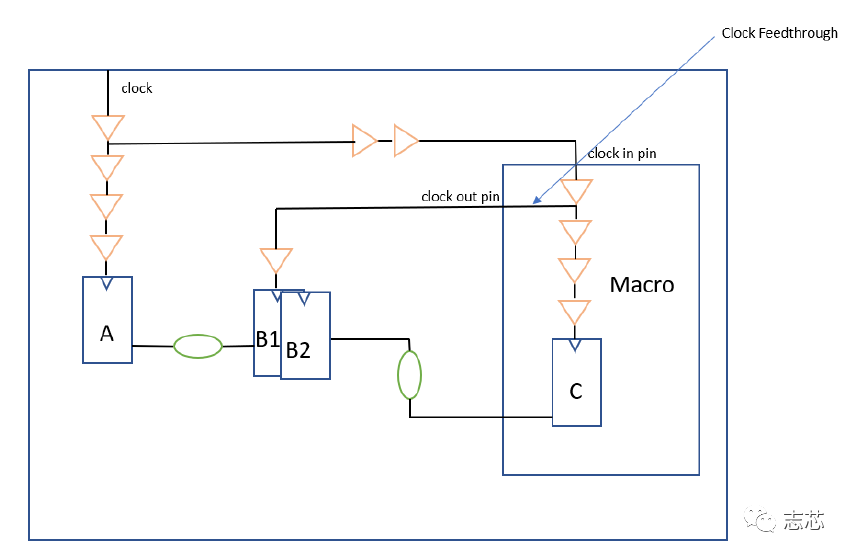

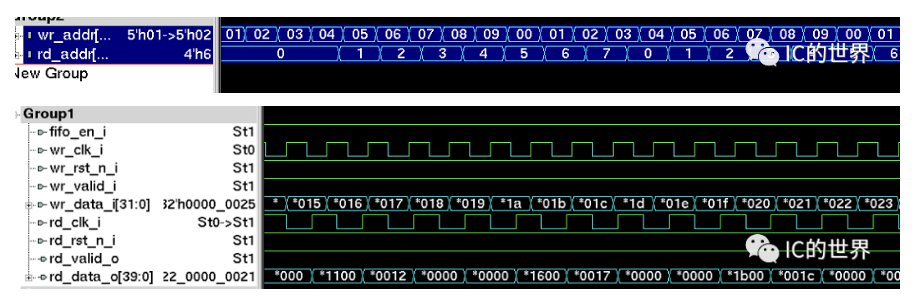

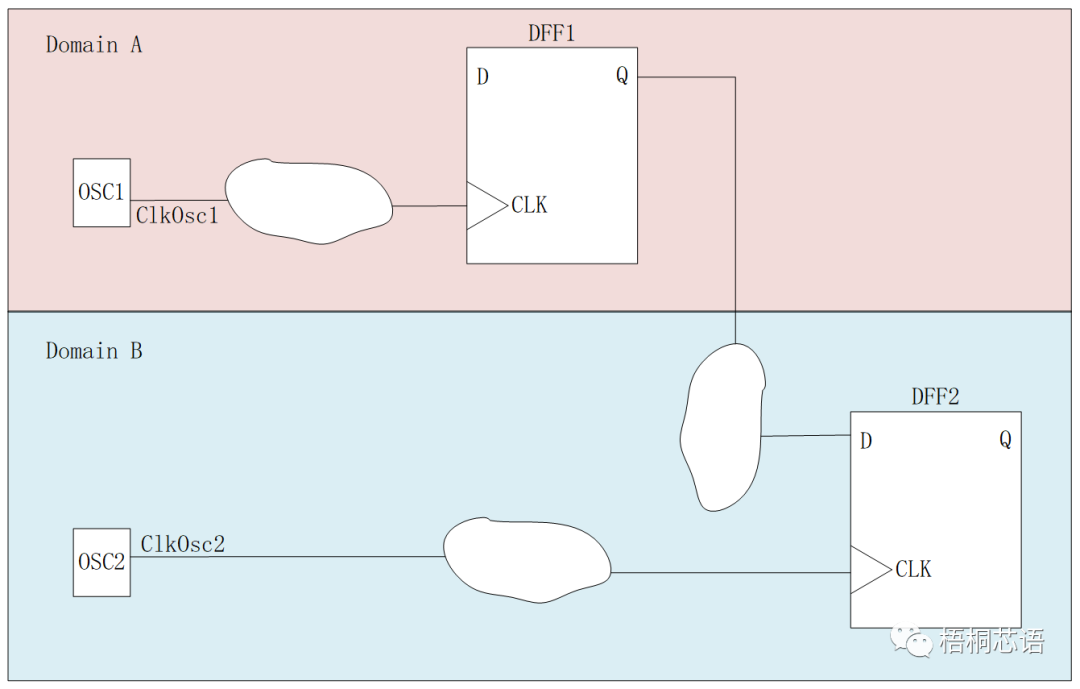

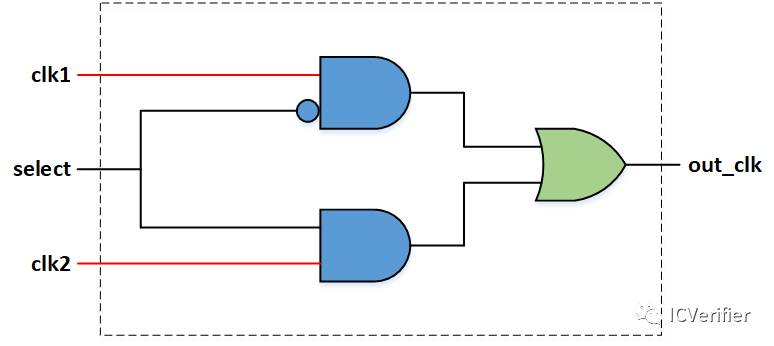

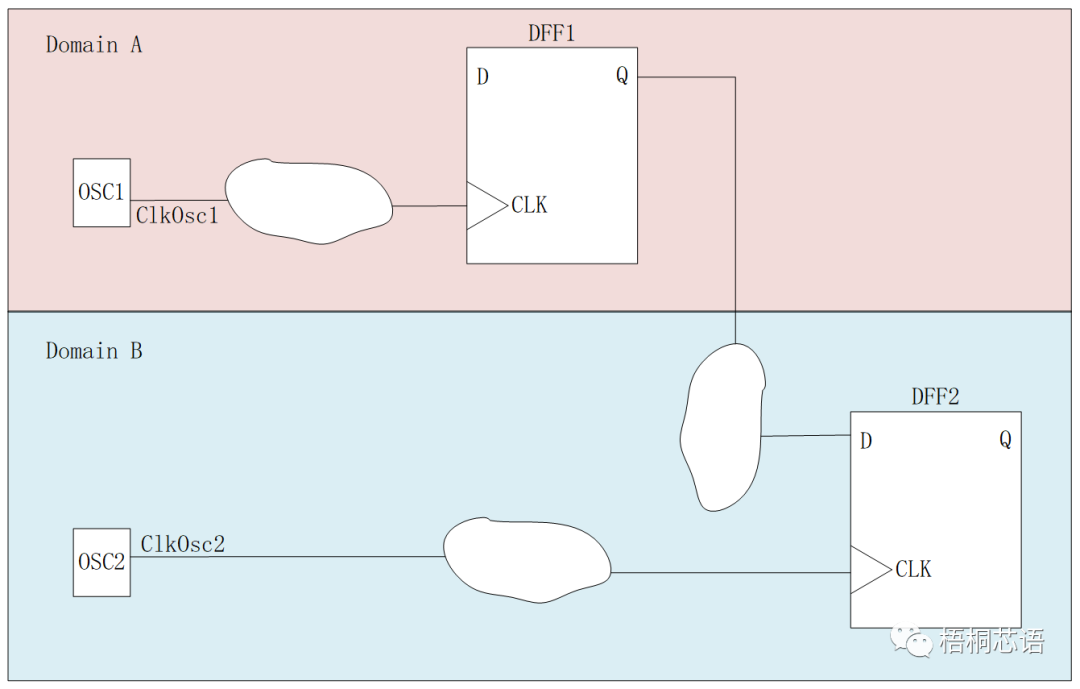

对于数字设计人员来讲,只要信号从一个时钟域跨越到另一个时钟域,那么就可能发生亚稳态。我们称为“跨时钟域”即“Clock Domain Crossing”,或CDC。

2024-01-08 09:39:56 174

174

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2023-12-29 09:29:50

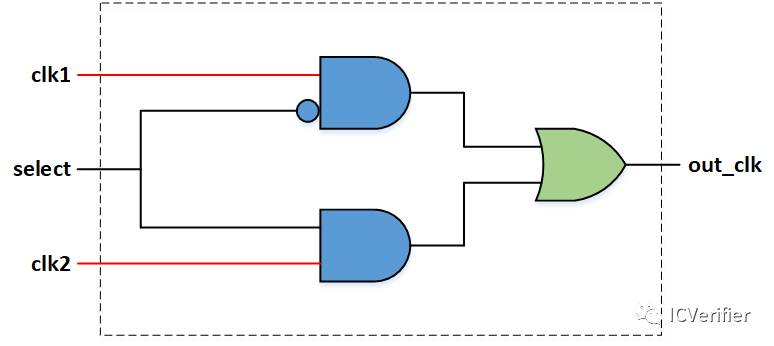

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

2023-12-14 15:28:56 257

257

LO这个使用的必要性在哪里,是否可被XTALN共源的方法完全取代?

[3] 目前我打算另外参考接到一片AD9520 PLL,直接输出两路信号分别给XTALN,这样的方案是否可以代替AD9361参考设计fmcomms5 中的 ADCLK846 + ADF5355 + 13617CF的方案?

2023-12-13 07:51:02

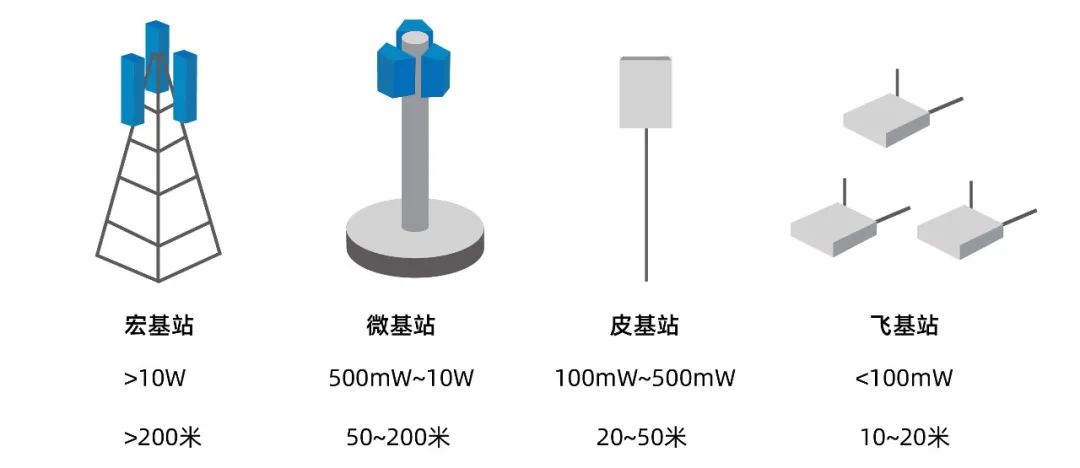

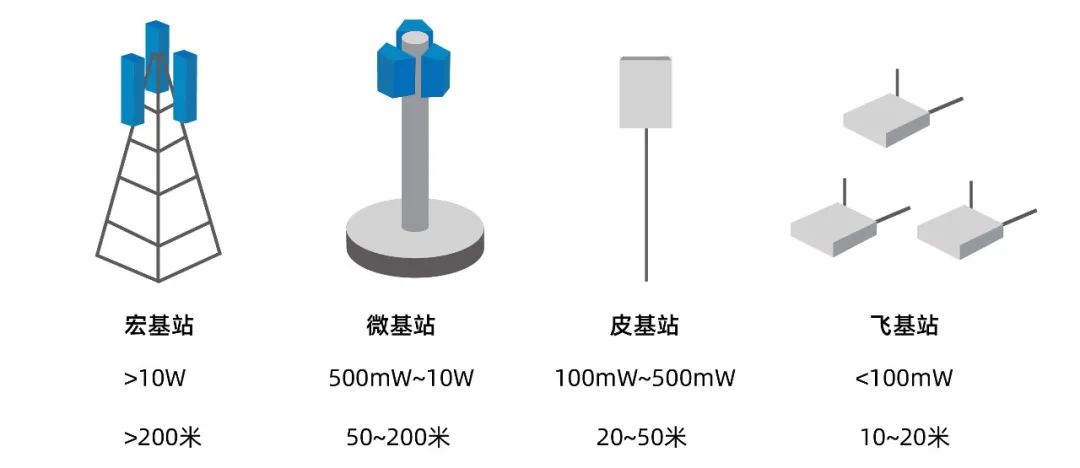

AC1571 是用于 5G 基站应用的基于 PLL的时钟发生器,该芯片采用全数字锁相环技术,以实现最佳的高频低相噪性能,并具有低功耗和高PSRR能力。典型应用场景:· 无线基站·

2023-12-12 14:25:17

当用SPI配置LTC2017或者LTC2108的时候需要注意什么?

因为我用fpga配置以上两个芯片,总是不能成功,而相同的主程序,配置ad9520,ad9510,ad9858等都可以。这些程序里面

2023-12-06 07:15:12

因项目需要将AD9510分配输出1GHz的时钟频率。参考时钟为50MHz。使用的VCO是CLV1000E-LF,调谐频率范围为900M~1100M,调谐电压为1V~10V。无论我怎样配置寄存器都不能

2023-12-06 07:05:21

案例分享:手工焊接导致IC和外围元器件受损

2023-12-05 10:13:51 220

220

为什么需要分段去做时钟树呢?因为在某些情况下,按照传统的方法让每一个clock group单独去balance,如果不做额外干预,时钟树天然是做不平的。

2023-12-04 14:42:18 524

524

的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。...

2023-11-28 14:33:57 0

0 二进制最佳接收原理 二进制最佳接收机的实现形式有哪两种? 二进制最佳接收原理是计算机通信中的重要概念,它是指在二进制通信中通过一定的方法,使接收机在信号传输过程中能够准确、可靠地接收到发送端传输

2023-11-27 16:19:07 422

422 浅谈5G小基站中时钟及无源射频器件的应用

2023-11-24 18:11:44 489

489

德赢Vwin官网

网站提供《如何实现AD7192的最佳辐射抗扰度性能.pdf》资料免费下载

2023-11-24 15:47:39 1

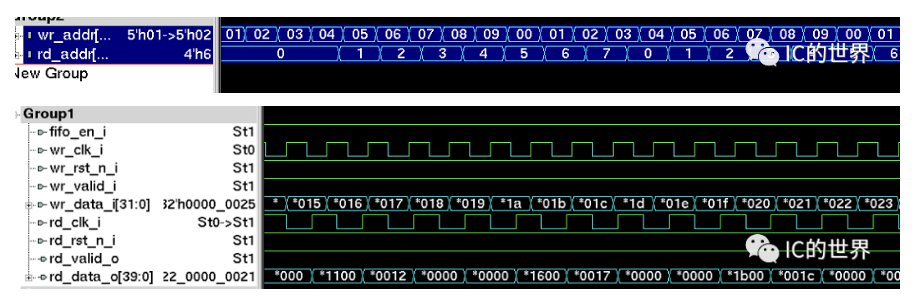

1 在进行模块设计时,我们经常需要进行数据位宽的转换,常见的两种转换场景有同步时钟域位宽转换和异步时钟域位宽转换。本文将介绍异步时钟域位宽转换

2023-11-23 16:41:59 337

337

使用可编程逻辑器件进行设计时,最关键的步骤之一就是为应用选择最佳的器件。

2023-11-15 10:03:35 515

515

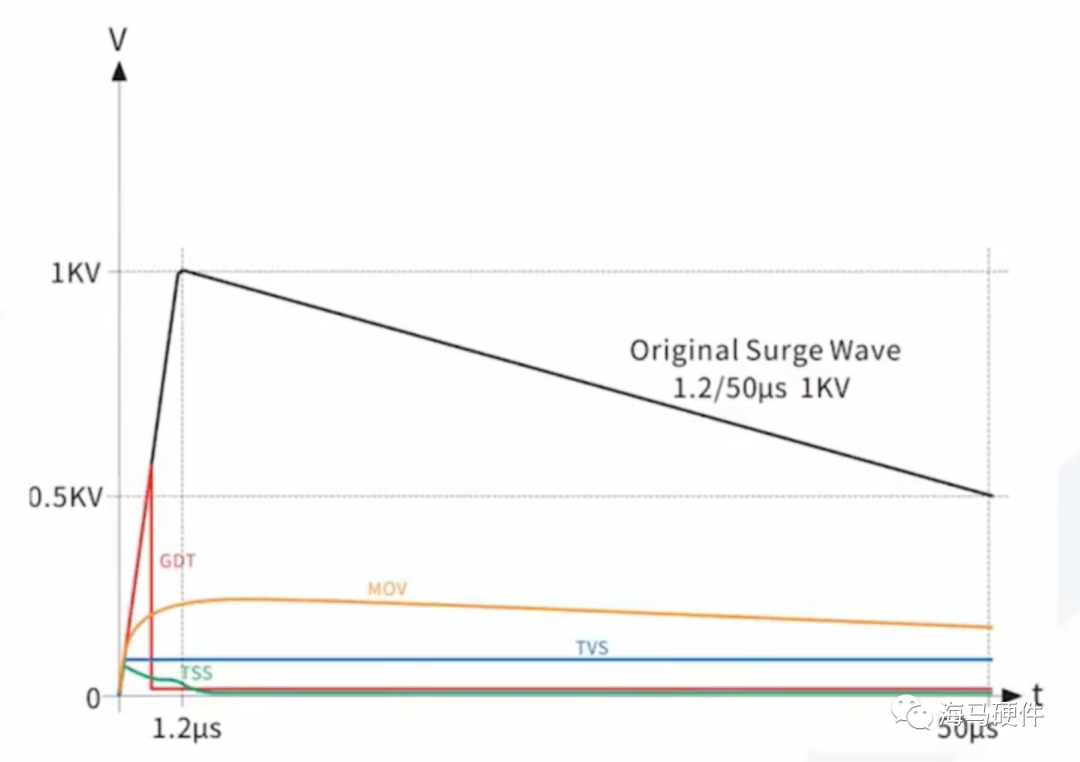

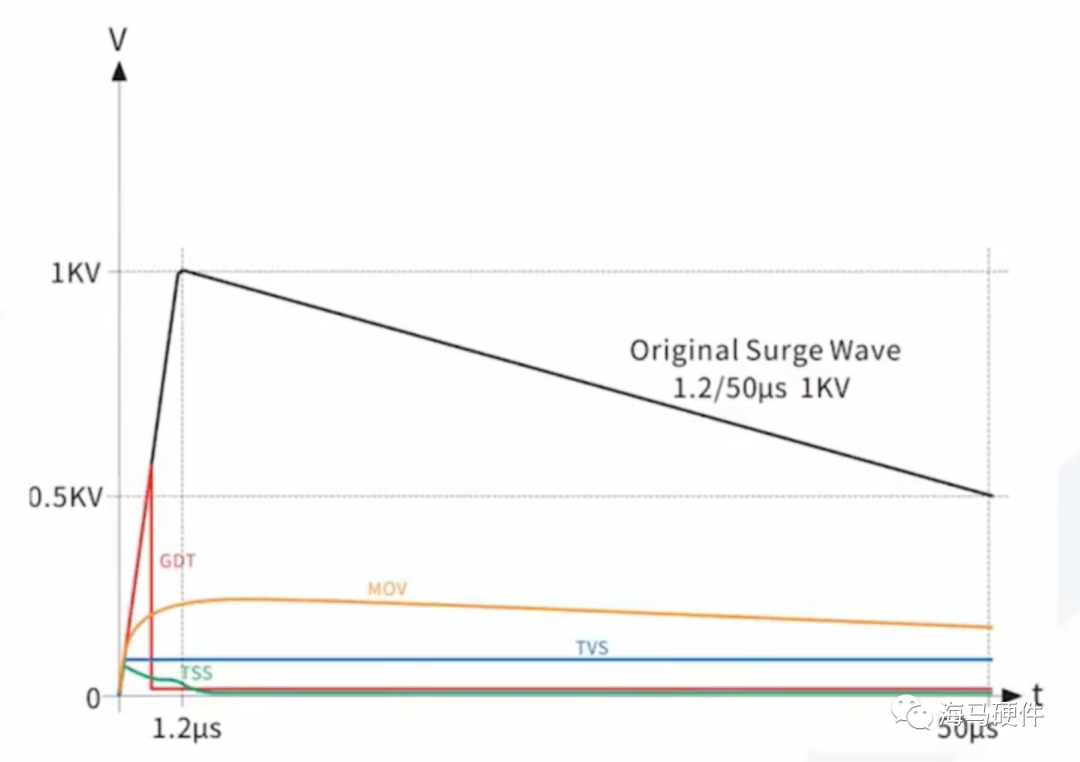

本文为EMC小知识学习简笔系列的 第四篇 ,前文EMC小知识学习简笔(三)介绍了数字IC电源、时钟、接口相关的滤波设计。接下来介绍 EMC防护中的主流防护器件 ,本文首先介绍 钳位型防护器件MOV、TVS ,下期为大家带来开关型防护器件GDT、TSS。

2023-11-10 09:14:39 1246

1246

时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26:56 298

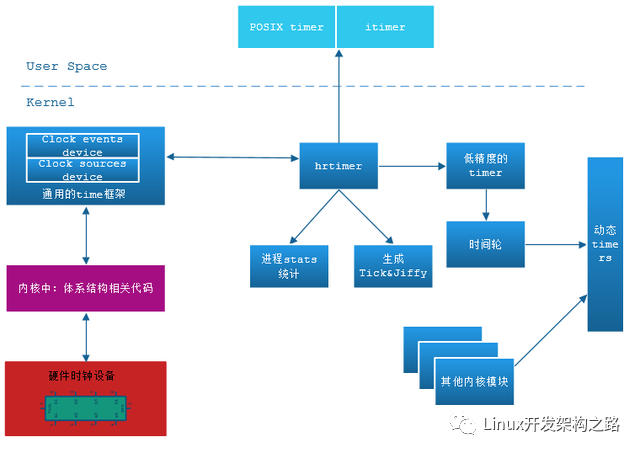

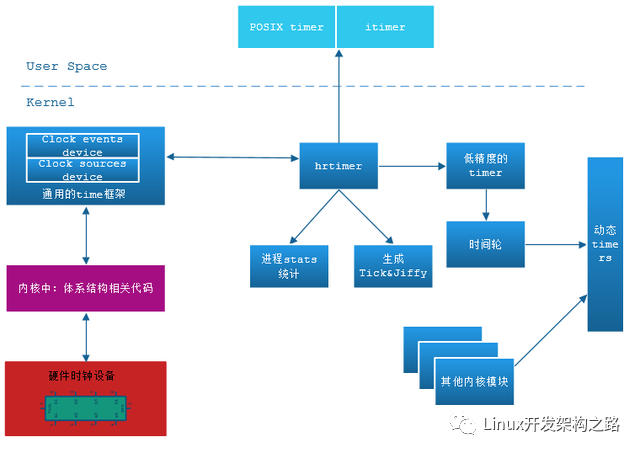

298 Linux内核时钟系统和定时器实现 Linux 2.6.16之前,内核只支持低精度时钟,内核定时器的工作方式: 系统启动后,会读取时钟源设备(RTC, HPET,PIT…),初始化当前系统时间

2023-11-09 09:12:12 480

480

时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 892

892

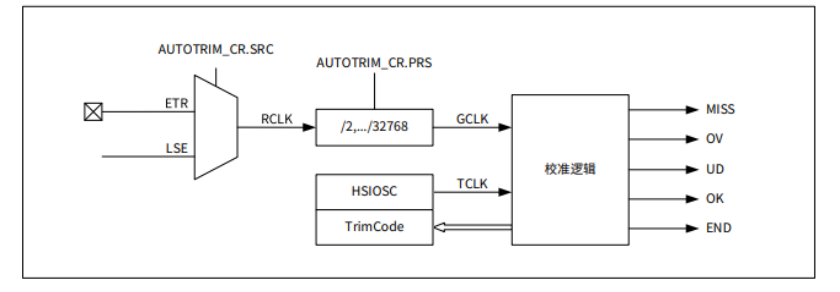

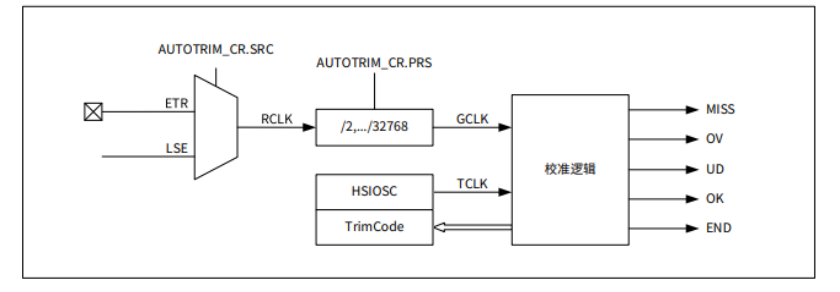

CW32L083如何实现AUTOTRIM时钟校准?

2023-11-07 17:17:37 221

221

FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢? FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据不同需要编程,实现不同的功能。在FPGA

2023-10-25 15:14:20 1037

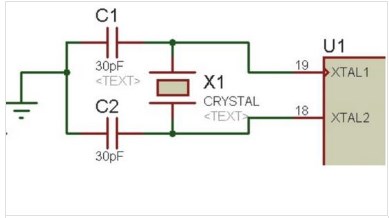

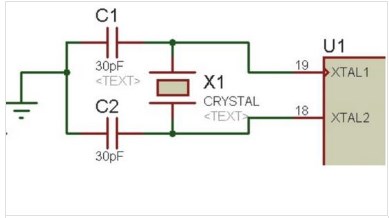

1037 嵌入式单片机开发的“时钟”是如何实现的? 嵌入式单片机时钟的概述 嵌入式单片机开发的“时钟”是一个基于晶振的计时设备,用于记录和管理时间的流逝。它通常包括时钟芯片、电源和控制器等组件,可以提供精确

2023-10-25 15:07:49 555

555

什么器件可以产生时钟信号?时钟信号是用来做什么用的?时钟信号起什么作用? 时钟信号是一个精确的电信号,它可以通过电子器件来产生,并且具有一定的频率和周期。时钟信号在电子系统中具有非常重要的作用,因为

2023-10-25 15:07:45 635

635 德赢Vwin官网

网站提供《IEEE1588时钟同步在PTN网中的实现.pdf》资料免费下载

2023-10-24 09:39:34 0

0 案例分享:手工焊接导致IC和外围元器件受损

2023-10-17 18:04:29 370

370

;SI5338Q-B-GMSi5338是一款高性能、低抖动的时钟发生器,能够在设备的四个输出驱动器中的每一个上合成任何频率。这个时间IC能够更换多达四个不同频率的

2023-10-17 17:02:33

IC元器件(集成电路元器件)是一种将多个电子元件(如晶体管、二极管、电阻、电容等)集成在一块半导体芯片上的电子元件。它具有多种基本功能。

2023-10-16 14:30:18 432

432 时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环

2023-10-13 17:39:50 443

443 德赢Vwin官网

网站提供《引脚可编程输出频率、输出逻辑电平及扇出功能的时钟分配电路.pdf》资料免费下载

2023-10-08 09:24:14 0

0 at89c51没有内部时钟,外部时钟可以不用晶振,用rc器件或者lc器件实现时钟输入吗

2023-10-07 08:38:55

C语言程序设计中,动态内存分配如何实现,需要注意哪些问题?

2023-09-28 16:53:41 799

799 在现代芯片中,芯片运行时有必要在两个不同的时钟之间切换。如果我们使用普通的多路复用器进行切换时钟会发生什么?

2023-09-20 10:53:27 865

865

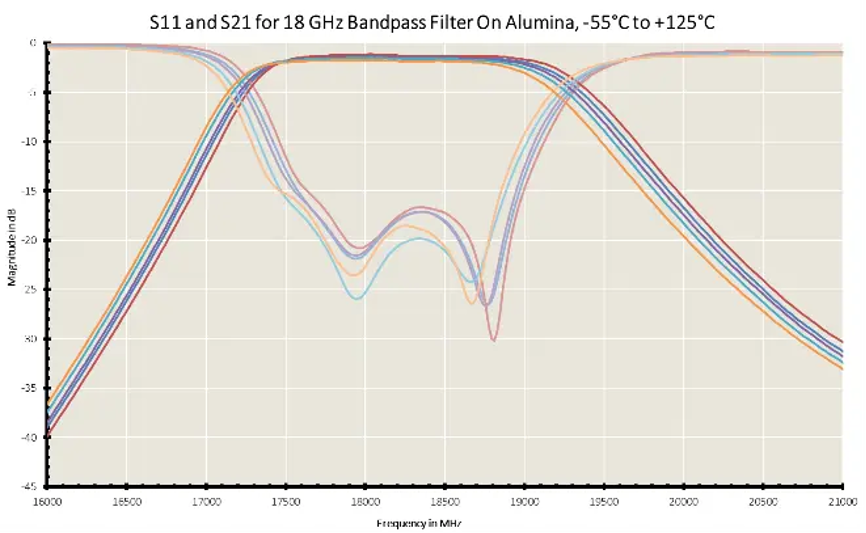

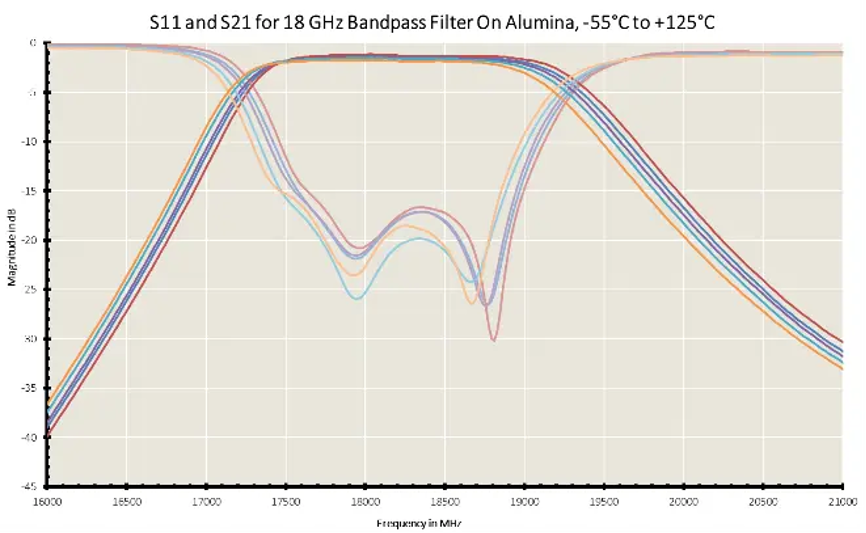

随着消费者和商业应用对快速通信需求的不断增长,射频器件的工作频率要求也变得越来越高,这给射频器件的设计师们带来了诸多挑战

2023-09-18 16:53:39 619

619

如何设计BUCK电路的最佳驱动? BUCK电路是市场上最常用的降压DC/DC转换器之一,它通过定期开关主电流来控制负载电压,以在不同负载条件下提供稳定输出电压。为了实现最高效和最稳定的转换,需要

2023-09-12 15:20:43 783

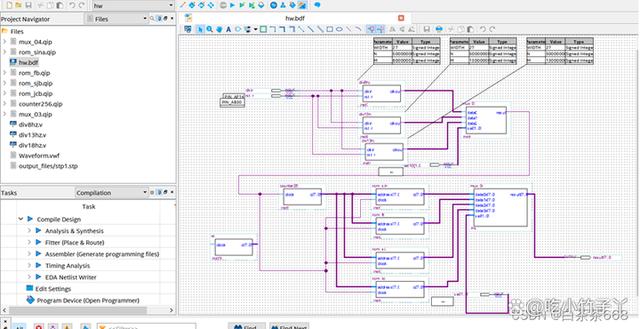

783 通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

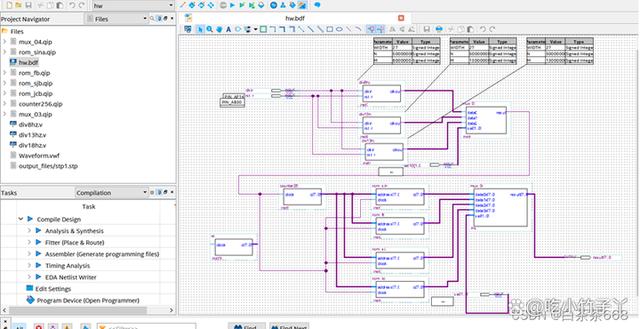

多功能信号发生器的原理框图如图所示。其中,CLKGEN是分频器,提供的50MHz的主频率进行分频,以得到满足多功能信号发生器设计需要的时钟频率。

2023-08-25 16:34:51 1291

1291

基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 0

0 通过采用新铁氧体材料实现面向NFC电路的最佳特性

2023-08-15 14:33:41 688

688

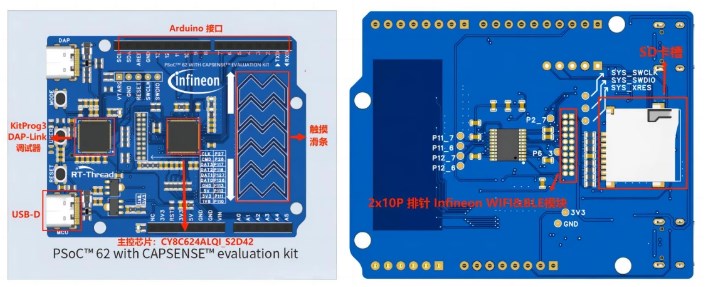

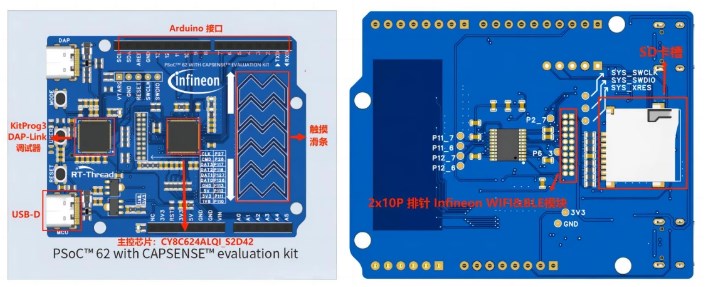

近年来,随着电子产品的发展,人们对时钟的要求越来越高。时钟系统是一种用数字电路技术实现年、月、日、周、时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。此时钟系统是基于posc6设计的,该系统包括了硬件电路部分和程序实现部分。

2023-07-31 14:51:22 562

562

在一个复杂的SoC(System on Chip)系统中,不可能只有一个时钟。我们一般认为,一个时钟控制的所有寄存器集合处于该时钟的时钟域中。

2023-07-13 17:39:52 1026

1026

9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-07-07 19:19:11 0

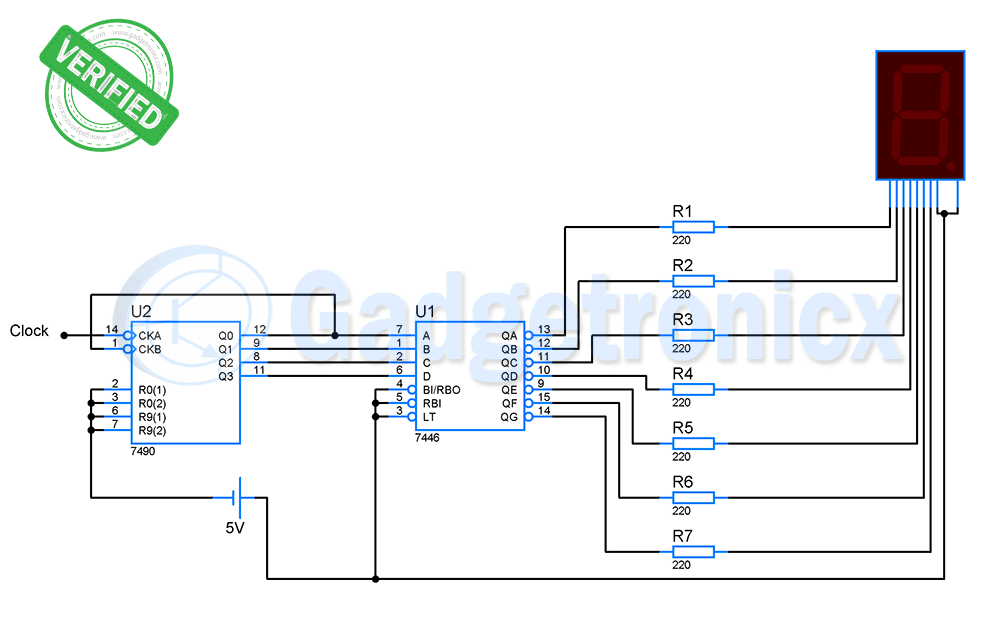

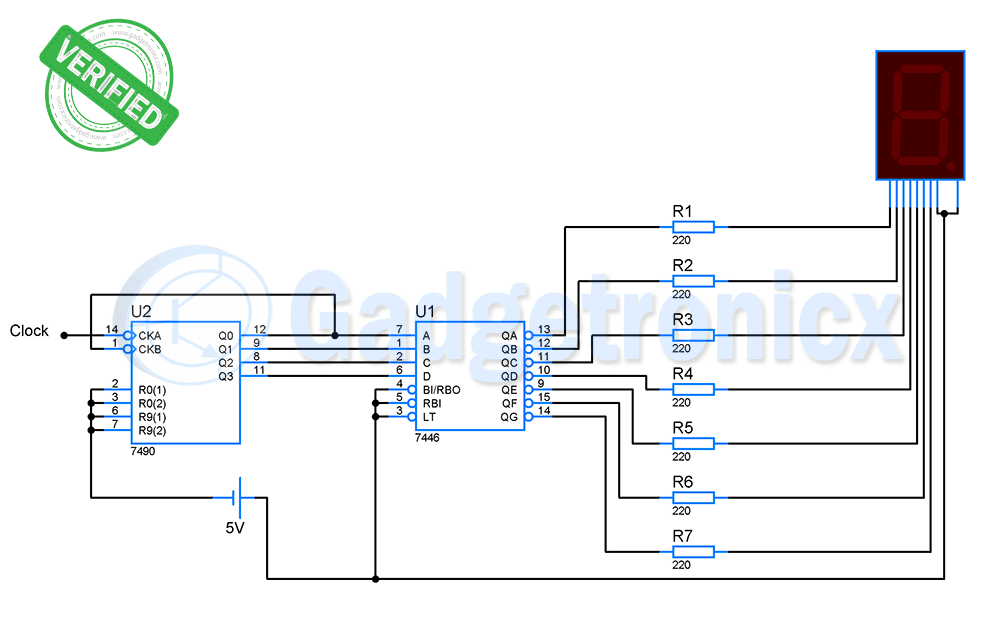

0 )和7446段解码器/驱动器IC1(IC7)工作。静态显示电路也可以用作计数器,通过控制时钟脉冲,而不是通过开关和《》段给出信号,从而显示发生的计数或事件的数量。

2023-07-05 15:51:15 1613

1613

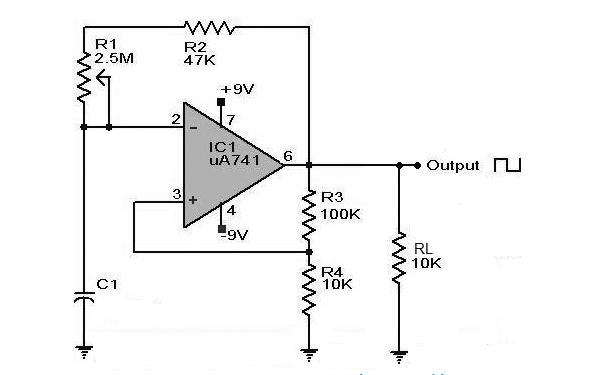

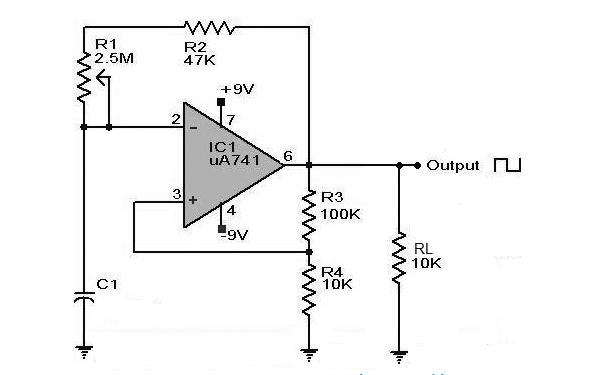

非稳态多谐振荡器具有重要意义,因此在各种电子电路中被广泛使用。大多数情况下,我们使用NE 555定时器IC作为非稳态多谐振荡器,但在此方波发生器中,我们使用运算放大器(Op-Amp)作为多谐振荡器。这个电路以非常简单的方式工作,建造一个非常便宜。

2023-07-03 10:31:28 800

800

RA9530/RA9520 Stylus 应用 AP 设计指南

2023-06-30 20:08:07 4

4 时钟门控(Clock Gating)** 是一种在数字IC设计中某些部分不需要时关闭时钟的技术。这里的“部分”可以是单个寄存器、模块、子系统甚至整个SoC。

2023-06-29 15:58:13 1014

1014

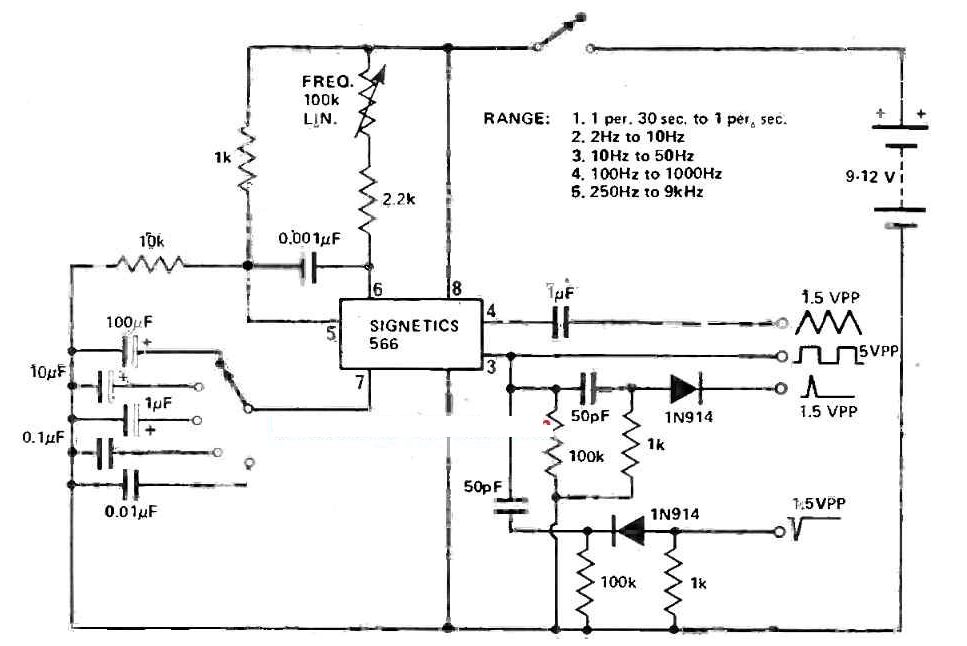

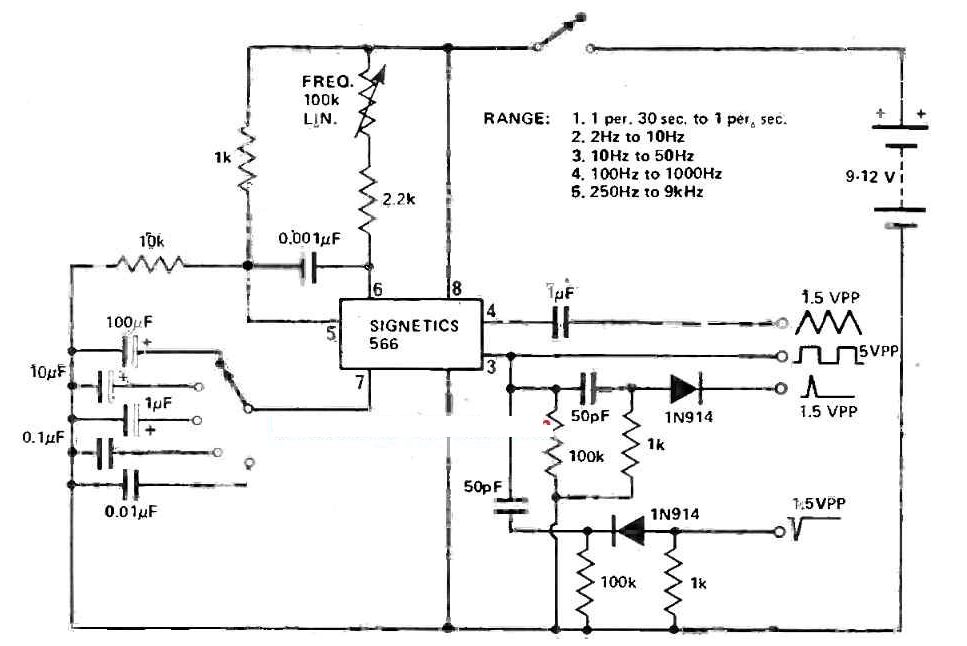

IC566非常适合借助其内部压控振荡器(VOC)构建测试发生器。该电路设计提供单独的输出,提供三角波和方波以及一组正向和负向尖峰输出。方波的振幅为5Vpk-pk,其余波形为1.5Vpk-pk。频率取决于连接到IC引脚7的电容值。

2023-06-02 17:26:28 493

493

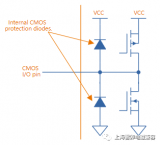

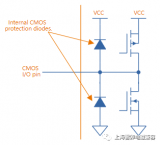

静电放电(ESD)是一种意外的快速高压瞬态波形,出现在电路内的导体上。ESD引起的高电压和电流峰值可能导致静电敏感IC等器件发生故障。

2023-06-02 09:21:45 390

390

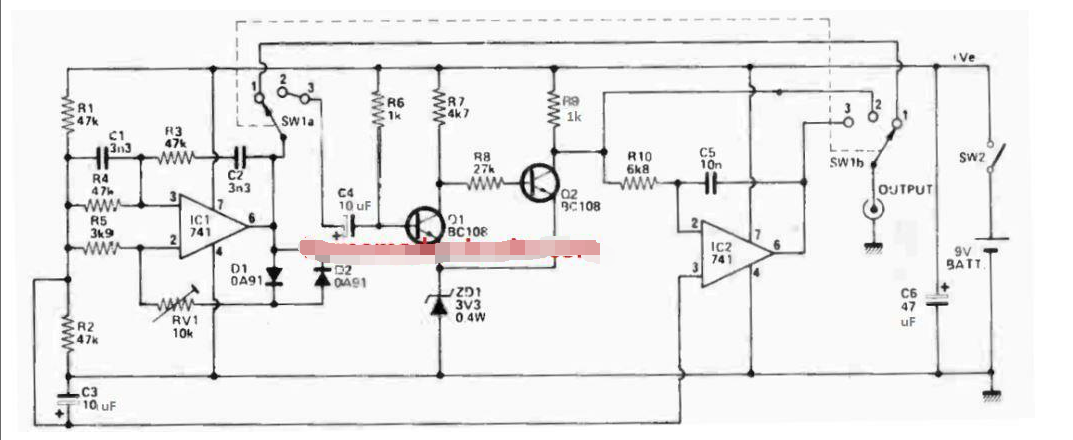

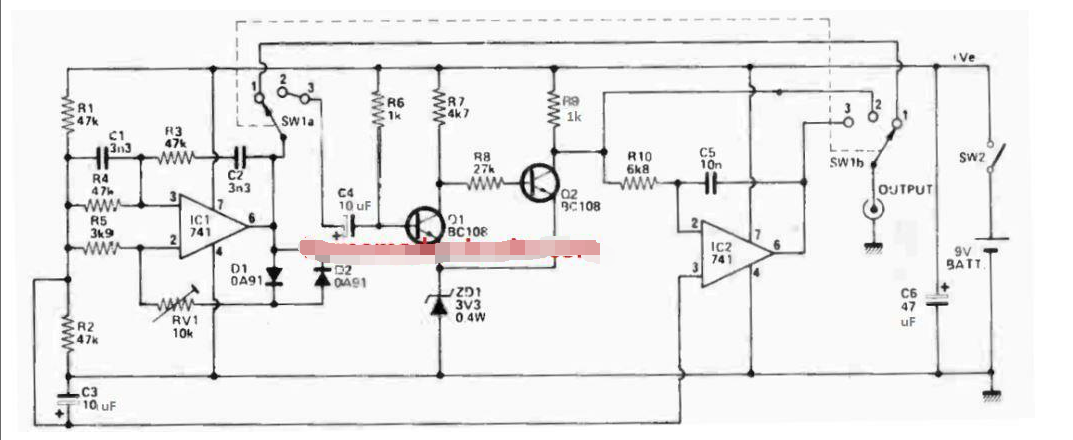

与典型的正弦波信号发生器相比,这种基于IC 741的函数发生器电路提供了更高的测试多功能性,同时提供1 kHz的方波和三角波,并且成本低且结构非常简单。看起来,方波的输出约为3V ptp,正弦波的输出约为2V rm.m.s。如果您想对被测电路更温和,可能会很快包括开关衰减器。

2023-06-01 18:16:48 620

620

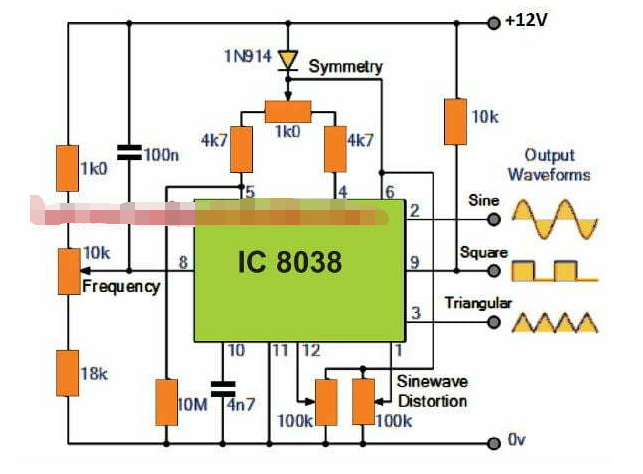

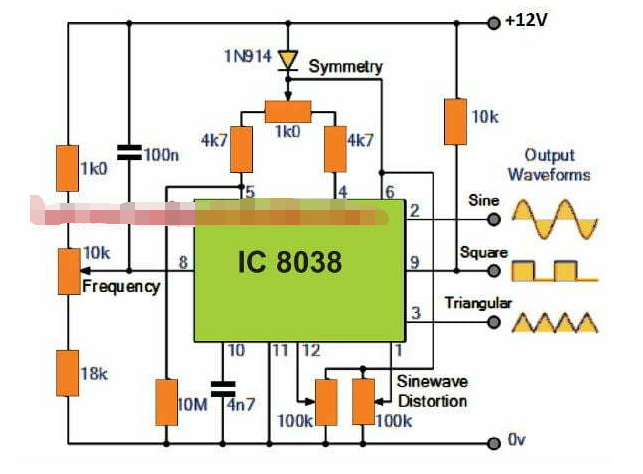

IC8038是一款精密波形发生器IC,专门设计用于创建正弦、方波和三角形输出波形,只需最少的电子元件和操作即可。

2023-05-31 18:10:57 914

914

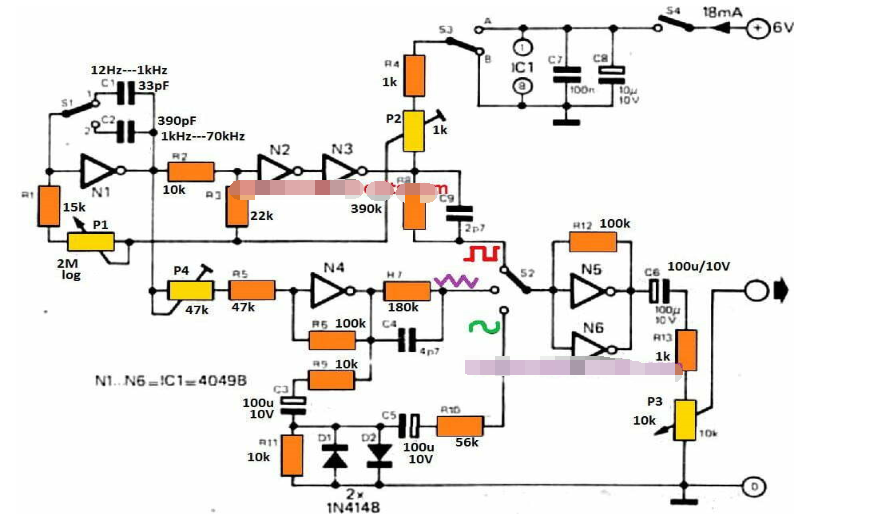

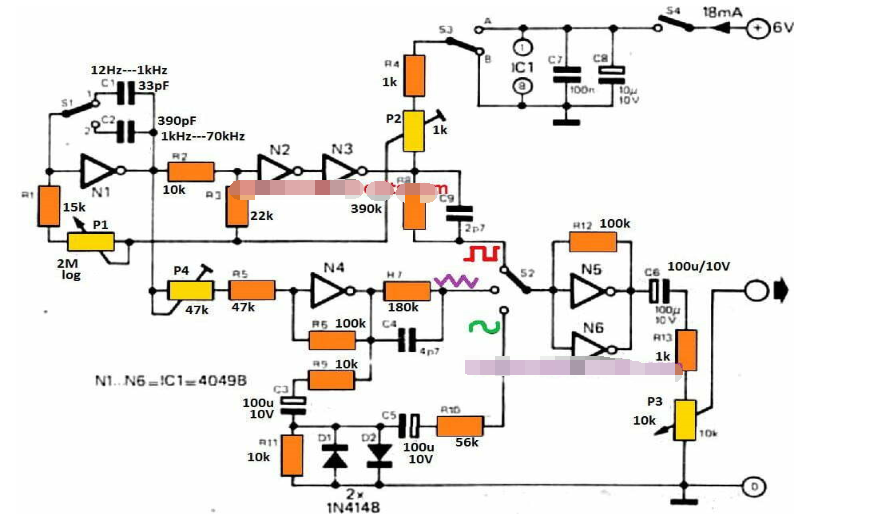

本文的目的是创建一个基本的、经济高效的开源频率发生器,它易于构建,可供所有业余爱好者和实验室专业人员使用。毫无疑问,这一目标已经实现,因为该电路提供各种正弦波、方波和三角波,并且大约 12 Hz 至 70 KHz 的频谱仅采用单个 CMOS 六角逆变器IC 和几个独立元件。

2023-05-31 17:42:20 845

845

IC设计就是指芯片设计。IC是“Integrated Circuit”的缩写,中文叫做“集成电路”,是指将多个器件和电路集成在一起,制成单个芯片,实现各种电子电路和系统集成的技术。IC设计的主要任务

2023-04-26 05:30:00 3366

3366 原文标题:谁说3DIC系统设计难?最佳PPAC目标轻松实现 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

2023-04-21 02:05:04 322

322

ISL9520EVAL1Z 用户指南

2023-04-18 19:58:06 0

0 随着数据速率的增加,链路抖动允许量变得越来越严格。硬件工程师将主要精力放在如何使他们的整个线路卡能够支持最大吞吐量,而为基准时钟产生的随机抖动分配尽可能小的允许量。针对基准时钟,对于一条25GbE

2023-04-17 10:37:30 357

357

展频IC在4M时钟上的应用

2023-04-14 10:12:27 0

0 大型时钟树使用多种类型的传输线,跨越多块电路板和多条同轴电缆,通过多个时钟器件路由时钟信号的情况并不少见。即使采用最佳实践做法,这些介质中的任何一种都可能带来大于10ps的相位偏差。然而,在一些

2023-04-12 11:26:14 262

262

本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 810

810

现代 DC-DC 转换器使用集成 MOSFET 的 PWM 控制器来实现 DC-DC 模块的最高功率密度。由于功率MOSFET位于PWM芯片内部,因此它们会显著影响器件的热性能。因此,为了获得最佳

2023-04-11 10:52:21 588

588

今天我们将讨论时钟如何影响精密 ADC,涉及时钟抖动、时钟互调和时钟的最佳 PCB 布局实践。

2023-04-11 09:13:22 644

644 大型时钟树使用多种类型的传输线,跨越多块电路板和多条同轴电缆,通过多个时钟器件路由时钟信号的情况并不少见。即使采用最佳实践做法,这些介质中的任何一种都可能带来大于10ps的相位偏差。然而,在一些

2023-04-06 14:22:35 914

914

在这篇文章中,我们将学习如何使用IC555创建6个有趣的警报器和警报音效发生器电路。

2023-04-02 09:58:10 2535

2535

BOARD EVAL AD9520-3

2023-03-30 11:41:51

BOARD EVAL FOR AD9522-1 CLK GEN

2023-03-30 11:41:49

BOARD EVAL FOR AD9522-2 CLK GEN

2023-03-30 11:41:49

BOARD EVAL FOR AD9522-3 CLK GEN

2023-03-30 11:41:49

BOARD EVAL AD9520-0

2023-03-30 11:41:48

BOARD EVAL AD9520-2

2023-03-30 11:41:48

BOARD EVAL FOR AD9520-5

2023-03-30 11:41:33

BOARD EVALUATION FOR AD9522-5

2023-03-30 11:41:33

BOARD EVAL FOR ISL9520

2023-03-30 11:41:33

BOARD EVAL FOR AD9522-0 CLK GEN

2023-03-29 22:55:18

BOARD EVAL FOR AD9520-1

2023-03-29 22:50:32

BOARD EVAL FOR AD9522-4 CLK GEN

2023-03-29 22:50:32

BOARD EVAL FOR AD9520-4

2023-03-29 22:50:31

时钟分配在数字系统中非常重要,因为数字系统需要不同的子系统使用相同的时钟参考。例如,在大多数情况下,基站的DSP部分必须与射频信号处理部分同步,锁相环(PLL)产生所需的本地振荡器频率,模数转换器

2023-03-29 11:03:45 1100

1100

大型时钟树使用多种类型的传输线,跨越多块电路板和多条同轴电缆,通过多个时钟器件路由时钟信号的情况并不少见。即使采用最佳实践做法,这些介质中的任何一种都可能带来大于10ps的相位偏差。然而,在一些

2023-03-29 02:15:02 348

348

12 LVPECL/24 CMOS输出时钟发生器,集成2 GHz VCO

2023-03-28 18:26:07

CDCM61002 1:2 超低抖动晶体时钟发生器

2023-03-28 18:26:06

14输出时钟发生器,集成2.0 GHz VCO

2023-03-28 18:12:38

时钟发生器 MSOP10 3~3.6V

2023-03-28 12:54:08

AM9520 - MICRO PERIPHERAL IC

2023-03-28 02:10:16

德赢Vwin官网

App

德赢Vwin官网

App

评论