,这使其在 AI 应用中面临着一些挑战。

Larzul 表示,想要解决这些问题的解决方案便是实现现场可编程门阵列 (FPGA),这也是他们公司的研究领域。FPGA 是一种处理器,可以在制造后定制

2024-03-21 15:19:45

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

FPGA芯片的主要特点包括以下几个方面: 高性能和实时性:FPGA芯片由数百万个逻辑单元组成,因此具有并行处理能力,其运行速度远超单片机和DSP。这种并行计算能力使得FPGA芯片在数据信号处理速度

2024-03-14 16:46:48 128

128 4 通道 16-bit DAC,2 个 QSFP+光接口用于通用无线接入。

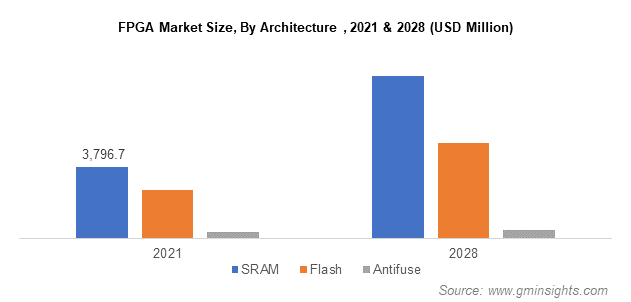

5G时代,FPGA 面临价提量升

价提:FPGA 主要用在收发器的基带中,5G 时代由于通道数的增加,计算复杂度增加

2024-03-08 14:57:22

客户想让我们把算法给到他们,由他们加到主机端的FPGA中这样可以降低整个设备的成本;但是客户这边反馈说他们家的主控也是FPGA可是跟我们使用的FPGA不是同一家的,遇到这种情况大家怎么处理?

2024-03-06 13:51:05

/Logos2/Titan2/Compa全系列,即将重磅上市!

本期推荐:盘古PGX系列PGX-MINI 4K开发板,基于紫光同创Compa系列低功耗CPLD。

产品详情

2024-03-01 19:02:59

/Logos2/Titan2/Compa全系列,即将重磅上市!

本期上新:盘古PGX系列PGX-MINI 4K开发板,基于紫光同创Compa系列低功耗CPLD。

产品详情

产品实拍

2024-03-01 15:16:13

Intel Agilex® F系列FPGA开发套件Intel Agilex® F系列FPGA开发套件设计用于使用兼容PCI-SIG的开发板开发和测试PCIe 4.0设计。该开发套件还可通过硬核处理器

2024-02-27 11:51:58

; Async 固件示例。

我们可以在应用程序中实现实时数据传输。 因此,我们选择使用GPIF II在我们的FPGA和USB控制器(CYUSB2014)之间实现从FIFO接口。

在C++软件端,识别“赛

2024-02-26 07:55:15

竞争冒险:在组合电路中,当逻辑门有两个互补输入信号同时向相反状态变化时,输出端可能产生过渡干扰脉冲的现象,称为竞争冒险。那么 FPGA 产生竞争冒险的原因是什么呢? 信号在 FPGA 器件内部通过

2024-02-21 16:26:56

OMAP-L138(定点/浮点DSP C674x+ARM9)+ FPGA处理器的开发板。

编写一个用于FPGA访问ChatGPT 4的程序代码是一个相当复杂的任务,涉及到硬件设计、网络通信、数据处理等多个

2024-02-14 21:58:43

的内存控制器,负责管理FPGA中的存储器。而EDMA是一种高速数据传输方式,可以让数据在内存和外设之间直接传输,提高通信效率。

接下来,我将用VHDL语言编写一个简单的程序,实现FPGA与ARM之间

2024-02-06 14:18:44

AurixTC2752的中端机制是怎么样的?有无固定的中端向量标号和中端地址啊?是类似于飞思卡尔或者28335那样的吗?

2024-02-05 06:33:09

维持在15上下一个很小的范围,达到稳压输出。

在这个电路中,有几个不明白的点。

1、输入端稳压管的作用,当输入电压相对于稳压管的稳压值较高时,稳压管是否还能维持其稳压值?

2、输出端加了一个二极管反接

2024-01-27 14:09:19

FPGA :通常具有少于10,000个逻辑单元。这类FPGA适用于简单、低成本的设计。

中规模FPGA :通常具有10,000到100,000个逻辑单元。它们适用于更复杂的设计,如嵌入式系统或特定领域

2024-01-26 10:09:17

最近有个项目,使用FPGA去驱动一些光耦、LED等信号,由于一些信号是同时输出的,导致FPGA的输出电流比较大,想问一下如何处理?能否通过在IO口输出端串接一些反相器或是缓冲器在去驱动光耦等。或是其他更好的方法?谢谢!

2024-01-08 22:26:41

本帖最后由 yonglong11 于 2024-1-4 11:29 编辑

FPGA,即现场可编程门阵列,作为可重构电路芯片,已经成为行业“万能芯片”,在通信系统、数字信息处理、视频图像处理

2023-12-28 14:18:28

D+/-后如何进行字节对齐?

在自时候总模式下,AD7626要求接收端能够动态的选择采样时钟相位,这在FPGA也是无法做到的。

请问有没有比较好的通过FPGA与AD7626对接的方案?

2023-12-22 06:34:25

最近在使用贵公司的AD9826芯片,用FPGA进行驱动,目前AD端输入模拟直流电压,未来要接光电装换的输入装置。现在用FPGA驱动时,在2-SHA模式下,电平转换侧的值时钟为FF,驱动AD的方法

2023-12-18 06:28:12

ADAS3022的单端输入、差分输入可以通过FPGA来设置吗,可以自由切换吗?

2023-12-14 07:04:30

咨询一个初级A/D问题:AD9684中DCO时钟的用法(FPGA控制)。AD9684与FPGA用LVDS模式接口互联时,FPGA端如何使用?手册中没有详细说明,是DCO上升沿捕获数据,作为数据同步

2023-12-13 09:01:52

AD7124-4想把AIN6引脚配置成单端输入,如何配置?通道寄存器,配置寄存器如何配置啊?

2023-12-08 06:48:28

分享。

这篇分享,涉及或需要了解下面的知识:

迪文COF智能屏基础了解

运行时内存中数据存储的原理

迪文DBUS GUI开发软件

串口指令的基本使用

串口传送图片数据的原理

电子相册的原理

Python

2023-12-06 15:58:58

国产有哪些FPGA入门?莱迪思半导体?高云半导体?

2023-12-05 16:05:38

ain0 - ain3配置为pt100温度采集,ain4 - ain7配置为单端信号输入,负端输入配置为AVSS。

采集温度时,ain4 - ain7通道关闭,内部基准关闭。采集ain4

2023-12-01 07:51:02

LTC2156-14有数据校验功能。寄存器A4所罗列的四种测试模式,在实际运行中均能正常校验通过。在A4寄存器的位数 1位是随机数据输出功能。请问这个随机数据输出模式主要用意是什么呢?能否用于校验

2023-11-30 08:13:55

;;

sw.Write(cc);

}

sw.Close();

计算的结果如下表:

从表中可以看出,此种方法可以计算出线段中任意一点的Y值。

但是次方法也存在着问题:

1,如果线段两端的Y值差别

2023-11-23 23:09:43

PAPT-B01葛尔莱法透气度测试仪PAPT-B01透气度测定仪是用本特生法(葛尔莱法、肖伯尔法可选)测试高分子材料、薄膜、纸张等空气透过量测定。可实现以下三种透气测定方法:本特生法:恒定压差

2023-11-23 11:54:49

初期这种特性尤为重要。

② 上市时间:由于 FPGA 买来编程后既可直接使用,FPGA 方案无需等待三个月至一年的芯片流片周期,为企业争取了产品上市时间。

③ 成本:FPGA 与 ASIC 主要

2023-11-20 18:56:02

电子、AI、数据中心。

安路科技(上海)

核心技术:全流程TD软件系统

主要产品:高端PHOENIX(凤凰)、中端EAGLE(猎鹰)、低端ELF(精灵)系列FPGA。

应用方案:LED显示屏、工业自动化

2023-11-20 16:20:37

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

。

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。当用户通过原理图或HDL

2023-11-03 11:18:38

ZYNQ器件中为1.8v。

(3) Vccpll为内部锁相环供电电压。

(4) Vcc_mio0为PS的MIO0 BANK的基准电压,VCCO_DDR为PS端的DDR的电压,此电压通常和选择的DDR颗粒

2023-11-03 11:08:33

ASIC 和基于处理器的系统的最大优势,它能够提供硬件定时的速度和稳定性,且无需类似自定制 ASIC 设计的巨额前期费用的大规模投入。但是和所有的数字电路一样,FPGA 电路中也存在毛刺问题。它的出现会

2023-11-02 17:22:20

你是否好奇过FPGA技术是如何影响日常使用的设备的?在当今快节奏的技术领域中,FPGA变得越来越重要。FPGA拥有强大的功能和广泛的应用,驱动着现代科技的进步。

2023-11-02 10:06:54 699

699 FPGA已成为现今的技术热点之一,无论学生还是工程师都希望跨进FPGA的大门。网络上各种开发板、培训班更是多如牛毛,仿佛在告诉你不懂FPGA你就OUT啦。那么我们要玩转FPGA必须具备哪些基础知识呢?下面我们慢慢道来。

(一) 要了解什么是FPGA

既然要玩转FPGA,那我们首先最重要的当

2023-10-27 17:43:33 413

413 摘要:莱迪思(Lattice )半导体公司在这应用领域已经推出两款低成本带有SERDES的 FPGA器件系列基础上,日前又推出采用富士通公司先进的低功耗工艺,目前业界首款最低功耗与价格并拥有SERDES 功能的FPGA器件――中档的、采用65nm工艺技术的 LatticeECP3系列。

2023-10-27 16:54:24 235

235 SLY-S1埃莱门多夫法撕裂度仪,采用埃莱门多夫法原理,适用于薄膜、薄片、软聚氯乙烯、聚偏二氯乙烯(PVDC)、防水卷材、编织材料、聚烯烃、聚酯、纸张、纸板、纺织品和无纺布等耐撕裂性的检测

2023-10-27 11:37:48

的接口。现在的低成本FPGA甚至可以满足大批量的应用。设计人员采用FPGA能够快速开发产品,以应对产品快速上市(市场要求缩短产品的开发时间)和远程更新的需求。 但是,把器件生产、现场更新和固件远程重构的工作外包可能会导致FPGA被复制、克隆或盗版。这对某些企

2023-10-24 15:50:02 415

415

大家好,我想请问一些关于写程序的问题(c语言)

我在网上看到的一些有关迪文屏的程序,里面的按键返回值的设置都有外设按键,所以不同的键值可以直接定义相反的状态,但如果没有外设呢?

例如:

sbitX

2023-10-18 07:22:09

FPGA的输入脚可以设置成斯密特触发器方式吗?

2023-10-16 06:36:15

,如果不满意,大可以拆了重新搭建,这个过程就叫做可编程逻辑,它改变了以往房子建造竣工之后便不能更改它的主体结构的局面。

在 FPGA 中,您通常会获得一些可重新配置的逻辑、一些用于保存正在使用的数据

2023-10-13 14:17:06

数据存储中的大小端指是什么意思

2023-10-13 06:20:00

资料简介:该源码是基于迪文DGUS屏与STC15系列单片机通信实战例程的迪文DGUS屏界面设计源码,用CorelDRAW X4软件设计,请使用相同版本软件或更高版本软件打开,关于该教程的详细内容大家

2023-10-09 08:56:29

资料简介:该源码是基于迪文DGUS屏与STC15系列单片机通信实战例程的完整教程PDF档,方便大家下载保存到电脑上离线查看

2023-10-09 07:43:17

仪器、机器视觉等领域。tl5728f-evm开发板的底板采用沉金无铅工艺的6层板设计,其核心板内部am5728通过gpmc总线与fpga通信,组成dsp+arm+fpga架构,开发板arm端主要

2023-10-09 07:26:55

。

Arm还能重铸当年荣光吗?更多人担忧Arm上市后的市场前景。从2016年被软银收购退市,到2023年再度上市,Arm面对的市场与竞争环境变了。

后疫情时代,消费电子市场整体疲软,移动端市场正全面处于下行

2023-09-30 12:22:15

安富莱STM32F103ZE-EK开发板原理图

2023-09-19 07:45:01

fpga中RTL simulation,打不开,但是我的modelsim,下载了呀,难道没有破解的原因吗?,并且我quartus软件,也把modelsim的路径引用了。

2023-09-08 23:46:58

FPGA作为一种逻辑芯片,硬件架构独特,具有并行性、低延时性和灵活性等特性,应用领域广泛。FPGA市场主要玩家是英特尔、AMD、莱迪思、Microchip、Achronix等;国内厂商包括复旦

2023-08-25 16:48:48 952

952

今天给大侠带来基于FPGA的扩频系统设计,由于篇幅较长,分三篇。今天带来第一篇,上篇。话不多说,上货。

这里也给出后两篇的超链接:基于FPGA的扩频系统设计(中)

基于FPGA的扩频系统设计(下

2023-08-23 16:32:43

EF4 器件是安路科技的第四代 FPGA 产品,基于 EF3 器件改进设计以满足汽车(Grade-2)应用,同时也能广泛应用于通信、工业控制和服务器市场。最多支持 279 个用户 I/O,满足客户板

2023-08-09 08:03:31

1. FPGA&CPLD 的下载

(1)生成位流文件(.sbit)后,可以把.sbit 文件下载到 FPGA 或 CPLD 中,首先将 JTAG下载器与 PCB 板连接并上

2023-06-26 10:52:38

的 PS 端通过 AXI4 总线与 PL 端进行通信,AXI4 总线协议具有高性能,高 频率等优势。在 Vivado HLS 中编写硬件代码时需要将输入图片,模型参数和边界框等 PS 端与 PL 端传递

2023-06-20 19:45:12

例程位置ZYNQ例程保存在资料盘中的Demo\\ZYNQ\\PL\\FPGA_DSP_GPIO文件夹下。DSP例程保存在资料盘中的Demo\\DSP\\XQ_GPIO_FPGA文件夹下。1.1.2

2023-06-16 16:02:47

,从而在相同的电路情况下实现了不同的逻辑功能。查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线

2023-05-30 20:53:24

)的一种。这个时间比著名的摩尔定律出现的时间晚 20 年左右,但是 FPGA 一经发明,后续的发展速度之快,超出大多数人的想象。

图 1 中给出了 FPGA 芯片的实物图:

图 1 FPGA

2023-05-30 20:40:25

很有可能综合不了,这就要求我们熟悉一些固定模块的写法,可综合的模块很多书上都有,语言介绍上都有,不要想当然的用软件的思想去写硬件。

4.学习习惯问题

FPGA学习要多练习,多仿真

2023-05-30 20:37:49

问题。

竞争冒险:在组合电路中,当逻辑门有两个互补输入信号同时向相反状态变化时,输出端可能产生过渡干扰脉冲的现象,称为竞争冒险。

那么 FPGA 产生竞争冒险的原因是什么呢?

信号在

2023-05-30 17:15:28

产品简介 高莱盒探测器数据采集模块是一个专门的软件和电子单元连接Golay 探测器与个人计算机通过 USB 接口连接。 它用于检测、处理和分析高莱

2023-05-24 10:28:39

我们正在开发基于 imx8mp 处理器的产品。它通过 i2c 总线将程序加载到莱迪思 CrossLink FPGA。FPGA 二进制数据大小(.ied 文件)为 149KB,使用 400 KHz

2023-05-16 06:28:53

FPGA系统设计中,如果用两个FPGA工作,应该如何设计两片之间的通信?从片的配置和时钟输入与主片有何不同?一个做主片用于数据处理和控制,一个做从片用于IO扩展。硬件和软件上应该如何设计两片之间

2023-05-08 17:18:25

所有的产品,直观的告诉你某个系列产品的应用场合。比如在Intel Altera的网站,就会明确标明它的三大类的FPGA产品,高端的Stratix系列,中端的Arria系列和低成本的Cyclone系列

2023-04-25 20:48:35

在放大电路中,输入端和输出端的电容起什么作用呢?

2023-04-25 11:06:41

FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

在FPGA的开发中,如何对inout信号进行赋值?

2023-04-23 14:25:00

如SPI接口中,FPGA通过模拟产生时钟和串行数据与一个外部芯片进行通信,其建立和保持时间是有时序要求的,这个时序要求可以通过外部的手册上获得。那么在FPGA中模拟这个接口要如何保证这个时序要求呀

2023-04-23 11:35:02

,拜托大家了!

FPGA系统设计中,如果用两个FPGA工作,应该如何设计两片之间的通信?从片的配置和时钟输入与主片有何不同

2023-04-23 11:31:45

在RL电路中为什么电阻两端与电感两端的电压和大于电源电压呢?

2023-04-21 16:21:15

MODULE USB-TO-FPGA TOOL W/MANUAL

2023-04-06 11:27:29

MODULE USB-TO-FPGA TRAINING TOOL

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN3

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN 3A

2023-04-06 11:27:11

的FPGA端引出的IO资源共97 个。CL1616并行模式采集需要的IO资源:数据线16个,控制线6个,合计22个。4片CL1616则需要IO资源共88个。因此,SOM-TLT3F的FPGA端最高可实现

2023-03-31 16:48:05

的sys_clk作为LED参考时钟。利用sys_clk(24MHz)进行计数,使LED按照0.5s的时间间隔进行状态翻转。图 2key_test案例案例说明案例功能:通过FPGA端用户输入按键USER4

2023-03-31 15:42:07

现场可编程门阵列 (FPGA) 是许多原型和中小批量产品的核心。FPGA 的主要优势是开发过程中的灵活性、简单的升级路径、更快的上市时间和相对较低的成本。一个关键的缺点是复杂性,FPGA 通常包含

2023-03-30 17:05:03 1408

1408 BOARD EVAL FPGA BLACKFIN EXTENDR

2023-03-30 12:06:40

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

G2-FPGA-BD-14-40-A-GEVK

2023-03-29 22:35:50

开拓者FPGA DEVB_121X160MM 6~24V

2023-03-28 13:06:25

新起点FPGA DEVB_90X128MM 6~24V

2023-03-28 13:06:25

我正在使用 i.MX RT 1064 MCU 通过 NXP 的 FlexSPI 控制器通过 Quad SPI 连接到莱迪思 FPGA。FPGA 正在处理我们的外围设备并将它从这些设备获得的测量

2023-03-27 06:23:57

德赢Vwin官网

App

德赢Vwin官网

App

评论