电池+STM8+RF433无线门锁时,如何既能保持RF433的数据接收,又能最低功耗待机

2024-03-18 07:13:38

为方便客户快速选型和验证WiFi模块,深圳市信驰达科技有限公司推出了WiFi开发板RF-WT01,支持适配信驰达RF-WM-ESP32B1、RF-WM-20CMB1、RF-WM-11AFB1、RF-WM-20DNB1 4款WiFi串口模块使用

2024-03-01 14:21:27 170

170

深圳捷扬微电子有限公司近日推出了一款革新性的超宽带(UWB)系统级芯片(SoC),型号GT1500。这款芯片以其极致的尺寸和功耗表现,成为目前全球最小、功耗最低的UWB SoC芯片。

2024-02-25 11:38:44 419

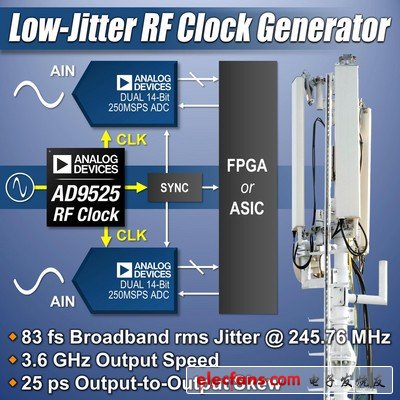

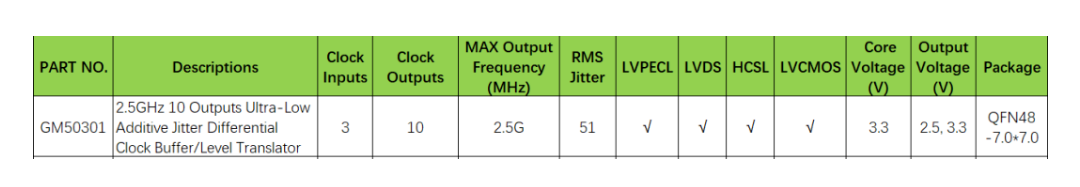

419 可以使用直流和交流耦合来提供。不仅限于JESD204B应用,14个输出均可单独配置为传统高性能时钟系统输出。 超低噪声时钟抖动消除器SC6301具有高性能

2024-02-19 09:41:40

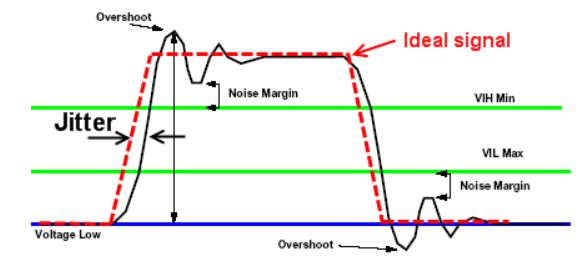

作者:Bill Schweber 投稿人:DigiKey 北美编辑 通过为系统组件确定步调,时钟振荡器为现代电路提供定时。随着系统速度提高到数百 MHz 或更高,这些时钟必须更快并具有极低的抖动

2024-02-13 17:47:00 621

621

德赢Vwin官网

网站提供《毫微微时钟网络同步器、抖动衰减器和时钟发生器RC32112A 数据表.pdf》资料免费下载

2024-01-31 10:09:17 0

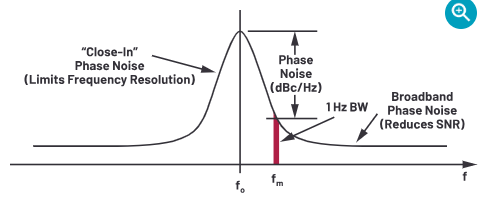

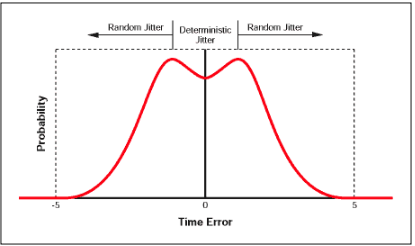

0 相位噪声与时间抖动有何关系?如何测试时间抖动? 相位噪声和时间抖动在信号处理中是两个非常重要的概念。它们都是衡量信号或系统的稳定性和准确性的指标。虽然它们在一些方面是相关的,但它们也有一些不同之处

2024-01-31 09:29:00 138

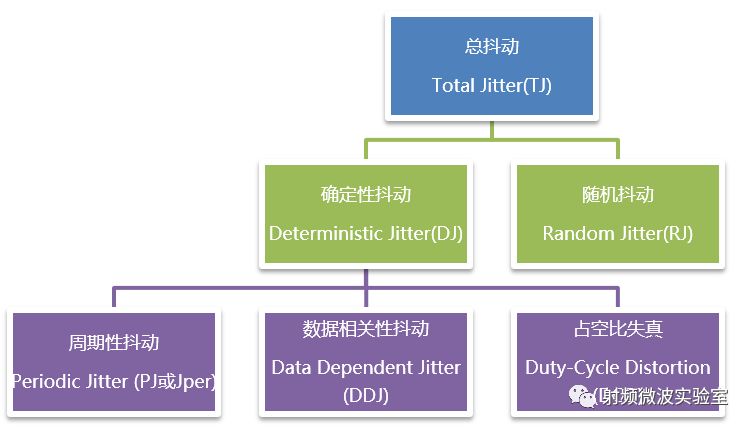

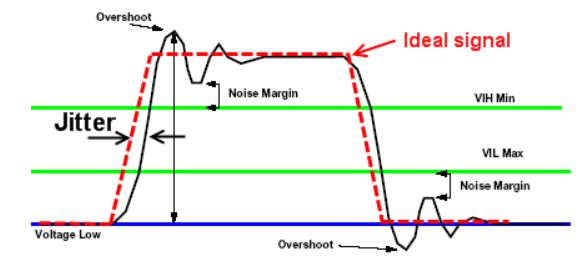

138 相位抖动是从哪来的?通信中有哪些抖动? 相位抖动是指信号在传输过程中产生的相位变化,导致信号的相位偏离理想值的现象。它是由多种因素引起的,包括时钟不准确、传输介质不稳定、信号传输路径不确定等。 时钟

2024-01-25 15:29:28 171

171 会导致晶振的输出频率出现一定的不稳定性,从而影响到系统的时钟同步和信号处理。相位抖动常常以皮克-到-皮克的相位偏移量来衡量,通常以ps级别或fs级别来表示。相位抖动在通信系统、时钟系统和高精度测量设备中都是非常重要

2024-01-25 13:51:07 126

126 ,包括时钟抖动、噪声抖动、跳变抖动和漂移抖动。 时钟抖动是指时钟信号在频率和相位上的变化。时钟信号是大多数电子系统中用于同步和定时的关键信号,其稳定性对系统的性能有着重要影响。时钟抖动会导致测量结果的不确定性

2024-01-19 15:01:31 253

253 德赢Vwin官网

网站提供《FemtoClock2抖动衰减器和时钟发生器RC325008A数据手册.pdf》资料免费下载

2024-01-14 10:55:06 0

0 的。那么如何解决呢?本文将对RF模组在Sleep状态下如何做到最低功耗进行说明。RF模组sleep时RF模组的IO状态先要获知RF模组Sleep时,RF模组的IO

2024-01-06 08:13:43 141

141

作者:Bill Schweber 时钟振荡器通过对系统组件进行起搏来提供现代电路的定时心跳。随着系统速度提高到数百兆赫兹 (MHz) 或更高,这些时钟必须更快并提供非常低的抖动(通常低于 100

2024-01-01 13:55:00 264

264

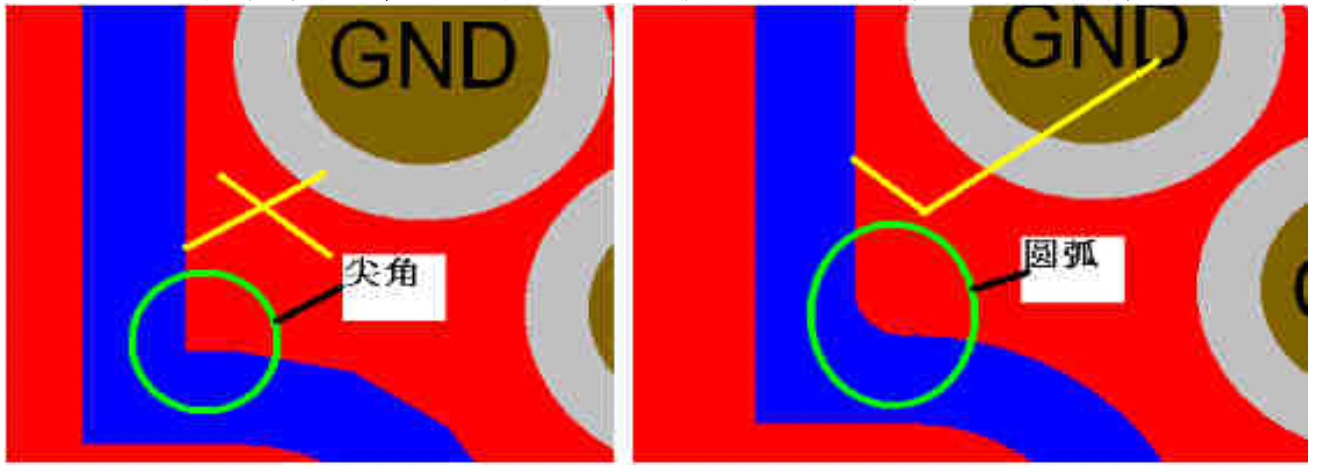

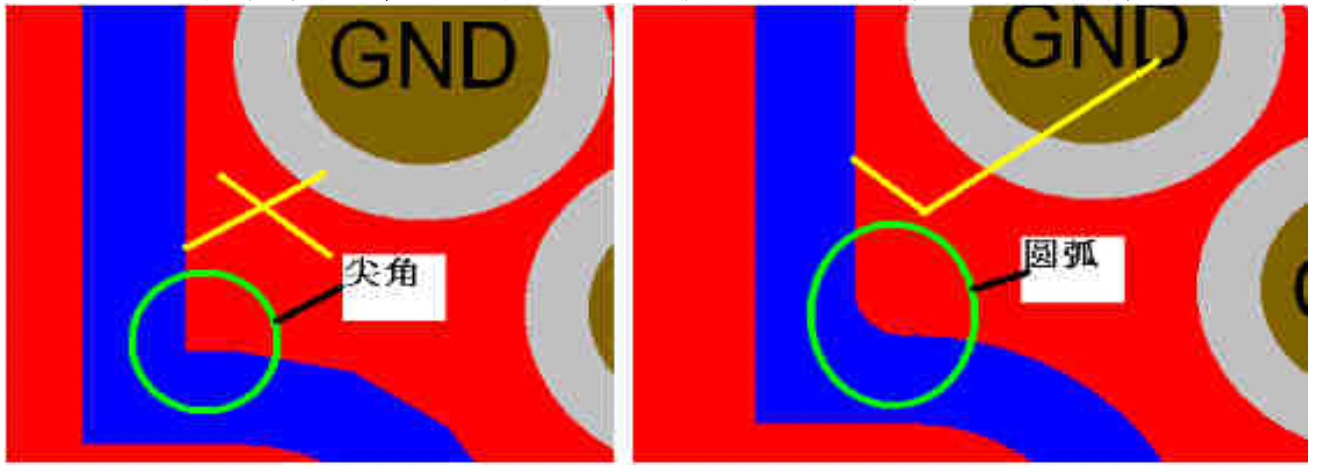

2.4GHz RF IC Layout guide

2023-12-20 10:20:22 225

225

各位专家:

对于Zedboard+AD-FMCOMMS1系统,采用Linux环境,制作一个FM收音机。

在IIO Oscilloscope中,本振LO频率设置为94.9MHz,AD9643的最低

2023-12-19 06:27:12

关于有源晶振的相位抖动和相位噪音

在通信网络、无线传输、ATM和SONET等高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至

2023-12-14 09:19:08

;以太网线卡,交换机和路由器· SCSI,SATA,and PCI-express· 低抖动,低相噪时钟发生器

2023-12-12 14:25:17

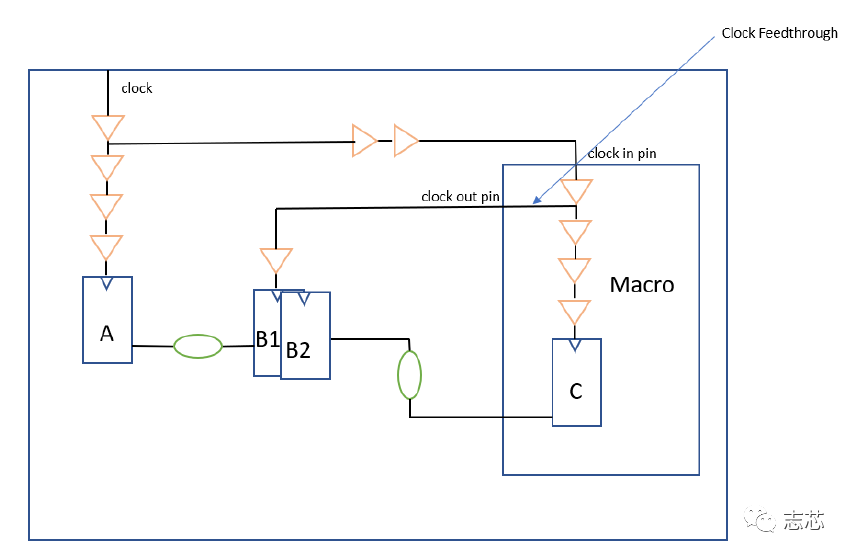

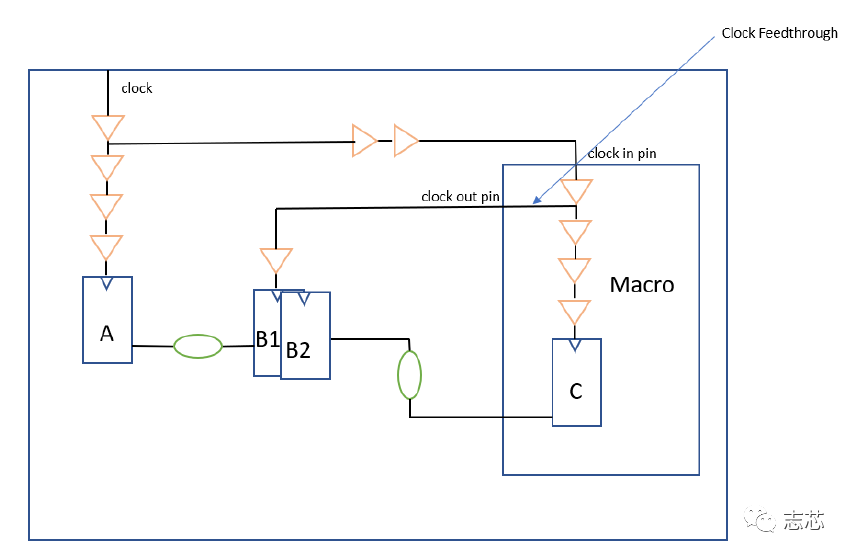

为什么需要分段去做时钟树呢?因为在某些情况下,按照传统的方法让每一个clock group单独去balance,如果不做额外干预,时钟树天然是做不平的。

2023-12-04 14:42:18 524

524

时钟抖动引起的采样噪声为:

计算SNR为:

为何这里不像《[MT-001_cn] 揭开公式(SNR = 6.02N + 1.76dB)的神秘面纱,以及为什么我们要予以关注》文章里那样,信号用

2023-12-01 08:30:52

天线到数字以及数字到天线……ADI公司凭借领先的射频技术能力、系统知识与工艺技术,提供直流到90 GHz以上、涵盖整个RF信号 链的最丰富多样的RF IC组合。ADI公司提供上千款高性能射频MMIC

2023-11-28 16:06:36 5

5 德赢Vwin官网

网站提供《时钟抖动对ADC性能有什么影响.pdf》资料免费下载

2023-11-28 10:24:10 1

1 1. 如果我想配置一个 48kHz 采样率,BCLK=48kHz * 4channel * 32bit = 6.144MHz的时钟 adi

2023-11-28 07:27:37

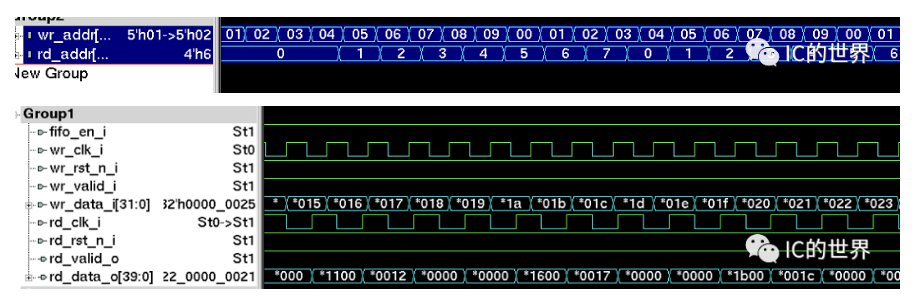

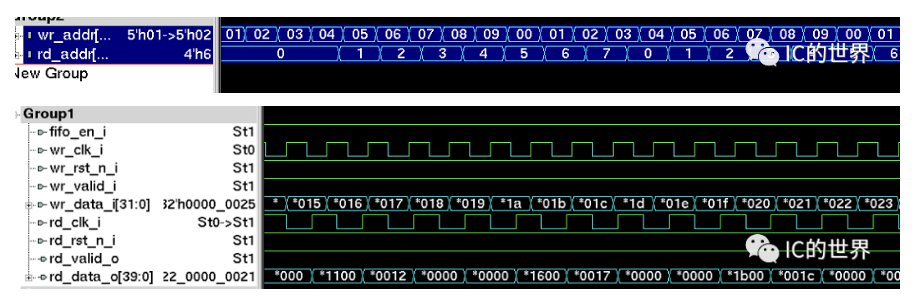

在进行模块设计时,我们经常需要进行数据位宽的转换,常见的两种转换场景有同步时钟域位宽转换和异步时钟域位宽转换。本文将介绍异步时钟域位宽转换

2023-11-23 16:41:59 337

337

时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 892

892

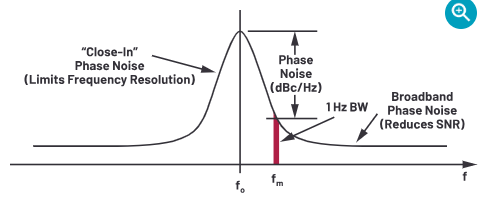

相位噪声和抖动是对时钟频谱纯度的两种表述形式,一个是频域一个是时域,从原理上来说,它们是等效的。

2023-10-30 16:02:46 686

686

相噪是与哪种类型的抖动相对应?如何理解相位噪声与时间抖动的关系? 相位噪声与时间抖动是两个在信号处理领域中经常涉及的概念。在讨论相位噪声时,我们常常听到相位噪声和时间抖动的联系。因此,本文将探讨相位

2023-10-20 15:08:11 556

556 德赢Vwin官网

网为你提供ADI(ADI)ADRV9002: Dual Narrow/Wideband RF Transceiver Data Sheet相关产品参数、数据手册,更有ADRV9002

2023-10-17 19:02:40

单片机如果外部直接输入时钟最低多少,比起10hz还是100hz,一般都是几mhz的,低频除了速度慢会有影响吗

2023-10-17 06:10:17

德赢Vwin官网

网为你提供ADI(ADI)HMC341LC3B SMT GAAs PHEMM MMI 最低NOISE AMPLIFIER, 21 - 29千兆赫数据表相关产品参数、数据手册,更有

2023-10-11 18:33:40

德赢Vwin官网

网为你提供ADI(ADI)ADAR5000: 17千兆赫至32千兆赫,4瓦RF分离器组合数据表相关产品参数、数据手册,更有ADAR5000: 17千兆赫至32千兆赫,4瓦RF分离器组合

2023-10-10 18:41:56

德赢Vwin官网

网为你提供ADI(ADI)ADP7156: 1.2 A, Ultralow 噪音,高PSRR,RF 线性监管数据表相关产品参数、数据手册,更有ADP7156: 1.2

2023-10-09 19:09:24

德赢Vwin官网

网为你提供ADI(ADI)ADTR1007: 6千兆赫至18千兆赫,前端IC数据表相关产品参数、数据手册,更有ADTR1007: 6千兆赫至18千兆赫,前端IC数据表的引脚图、接线图、封装

2023-10-09 18:50:34

德赢Vwin官网

网为你提供ADI(ADI)AD9084: 阿波罗MxFE Quad, 16比特, 28 普普惠战略(普惠战略)RF 发援会和夸德, 12比特, 20 普惠战略(普惠战略)RF ADC初步

2023-10-09 18:45:52

德赢Vwin官网

网为你提供ADI(ADI)AD9088: 阿波罗MxFE Octal, 16Bit, 16PSS RF DAC和Octal, 12Bit, 8 PSS RF ADC初步数据表相关产品参数

2023-10-09 18:45:25

在低速转动是抖动比高速抖动厉害,怎么让低速不抖动

2023-10-08 07:30:38

德赢Vwin官网

网为你提供ADI(ADI)AD9361S-CSH:RF Agile收发机数据表相关产品参数、数据手册,更有AD9361S-CSH:RF Agile收发机数据表的引脚图、接线图、封装手册

2023-10-07 17:53:03

时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。

2023-09-11 10:55:34 502

502

电机抖动大怎么解决 电机抖动大是指在电机运转时发生了震动或抖动现象,它主要是由于电机失衡、机械系统不稳定、设计误差或部件故障等因素造成的。如果不及时解决,电机抖动大不仅会降低设备的工作效率和寿命

2023-08-28 18:24:06 2921

2921 真正的无毛刺监控器IC是存在,MAX16161/MAX16162就是例子,即使在零电源电压下,这些IC也能产生可靠的复位信号,从而能够监控供电电压低于1V的电子器件。 可靠的监控器IC始终是工业界

2023-08-14 09:10:02 255

255

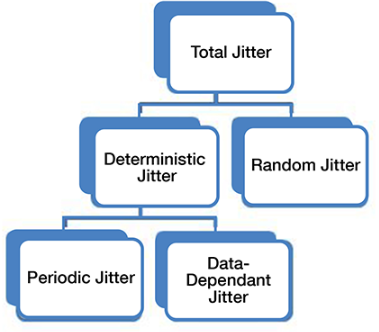

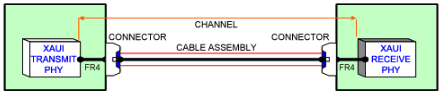

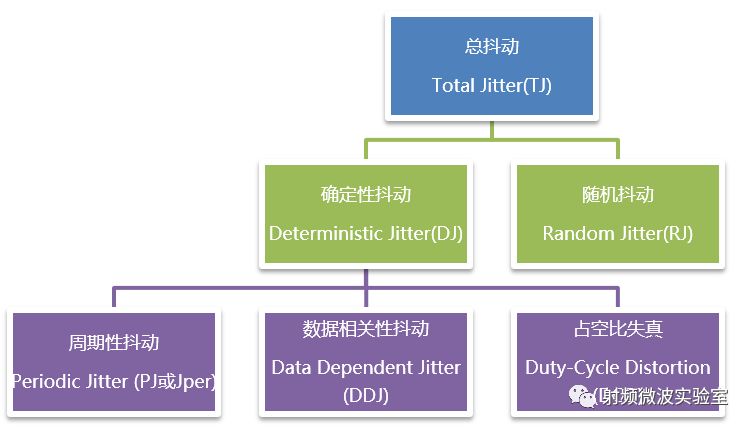

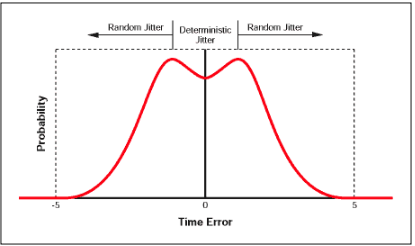

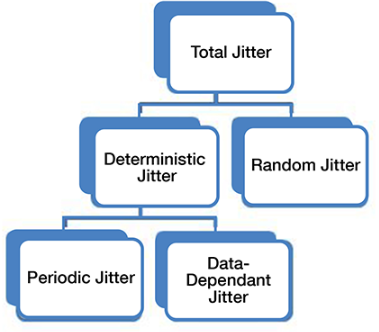

随着通信系统中的时钟速率迈入GHz级,抖动在数字设计领域中日益得到人们的重视。在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

2023-08-11 09:34:01 3557

3557

随着通信系统中的时钟速率迈入GHz级,抖动在数字设计领域中日益得到人们的重视。在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

2023-08-11 09:33:28 533

533

真正的无毛刺监控器IC是存在,MAX16161/MAX16162就是例子,即使在零电源电压下,这些IC也能产生可靠的复位信号,从而能够监控供电电压低于1V的电子器件。 可靠的监控器IC始终是工业界

2023-08-08 18:10:01 323

323

电池+STM8+RF433无线门锁时,如何既能保持RF433的数据接收,又能最低功耗待机

2023-08-07 09:19:31

产品概况: SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7

2023-07-25 17:06:53

德赢Vwin官网

网站提供《PI6C5913004最低输出抖动缓冲器IC 确保40GE/100GE设计性能.pdf》资料免费下载

2023-07-25 14:45:10 0

0 、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2023-07-24 11:07:04 655

655

的供应商,拥有遍布世界各地的60,000客户,涵盖了全部类型的电子设备制造商。作为领先业界40多年的高性能模拟集成电路(IC)制造商,ADI的产品广泛用于模拟信号和数字信号处理领域。公司总部设在美国马萨诸塞州诺伍德市,设计和制造基地遍布全球。ADI公司被纳入标准普尔

2023-07-12 09:15:02 217

217

抖动jitter的有关概念和理论很多,容易把人抖晕;本文目的是帮助产品研发和测试工程师,不需要研究时频域抖动测量的原理和公式,只讲用什么手段测抖动,以及测试值的表达含义。

2023-07-07 17:30:08 2689

2689

本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 959

959

在本例中,我们将研究如何利用低抖动时钟发生器AD9643对双通道14位250 MSPS ADC进行计时。使用这些特定产品的常见时钟频率为9523.245 MHz,因此我们将为AD76使用30.72 MHz基准电压源(外部振荡器),并设置内部寄存器,为AD9523生成低抖动时钟输出。

2023-06-30 16:59:52 798

798

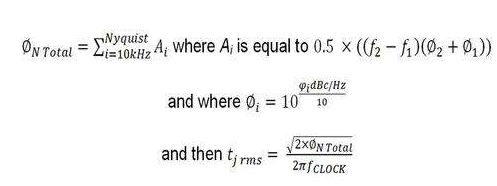

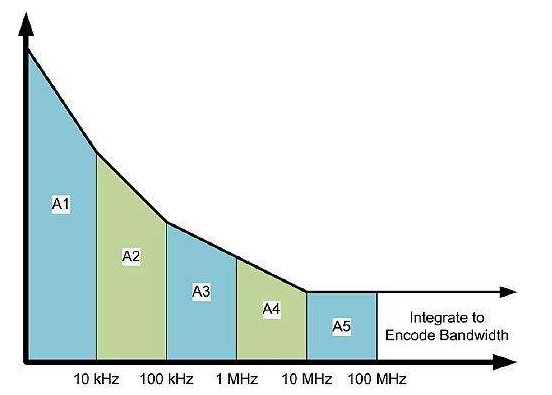

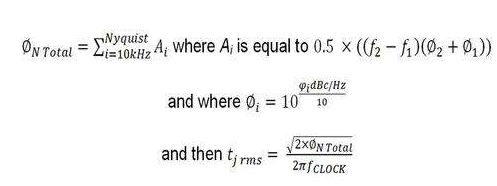

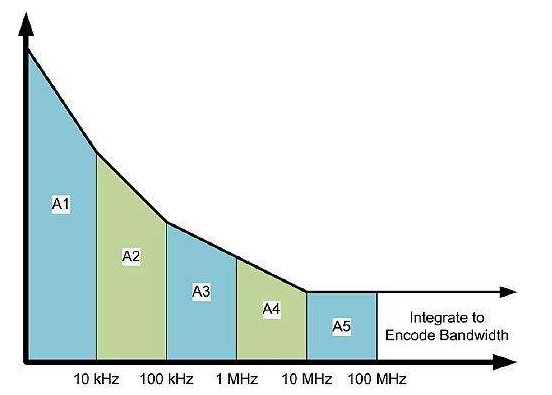

这是为数不多的跨越围栏是有利的情况之一。目前市面上的许多时钟产品都指定器件的相位噪声,而不指定抖动。让我们来看看如何从相位噪声变为抖动。然后,我们将能够预测具有一定抖动的ADC的SNR。一个例子将不得不等待,因为我在这里只有这么多空间。现在让我们专注于数学。下图显示了我们如何根据时钟源的相位噪声计算抖动。

2023-06-30 16:58:01 566

566

新品速递 全球半导体解决方案供应商瑞萨电子(TSE:6723)宣布面向新兴的DDR5 DRAM服务器和客户端系统推出客户端时钟驱动器(CKD)和第三代DDR5寄存时钟驱动器(RCD)。凭借这些全新

2023-06-29 18:15:03 359

359 时钟门控(Clock Gating)** 是一种在数字IC设计中某些部分不需要时关闭时钟的技术。这里的“部分”可以是单个寄存器、模块、子系统甚至整个SoC。

2023-06-29 15:58:13 1014

1014

的供应商,拥有遍布世界各地的60,000客户,涵盖了全部类型的电子设备制造商。作为领先业界40多年的高性能模拟集成电路(IC)制造商,ADI的产品广泛用于模拟信号和数字

2023-06-29 10:00:22 232

232

的供应商,拥有遍布世界各地的60,000客户,涵盖了全部类型的电子设备制造商。作为领先业界40多年的高性能模拟集成电路(IC)制造商,ADI的产品广泛用于模拟信号和数字信号处理领域。公司总部设在美国马萨诸塞州诺伍德市,设计和制造基地遍布全球。ADI公司被纳入标准普尔

2023-06-28 09:10:02 159

159

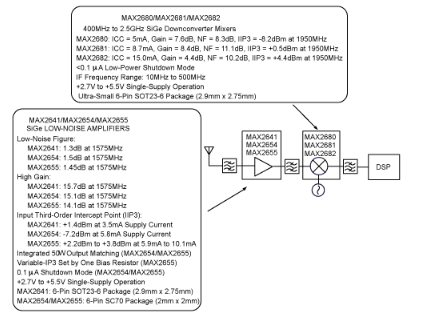

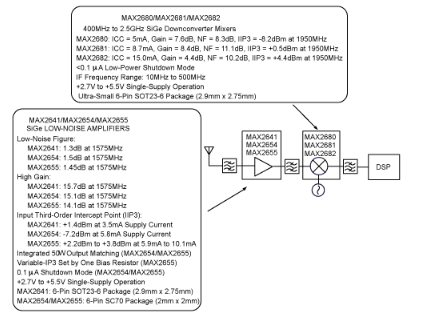

ASIC,但缺乏RF-IF前端,用于将传输的GPS频率下变频为低IF频率。ADI公司已经生产了几款RF IC,事实证明它们是完成这些任务的绝佳选择。

2023-06-26 17:29:41 338

338

当使用按钮手动复位微处理器 (μP) 时,按下和取消按下开关时,来自开关的振铃可能会导致错误的复位输出信号。Maxim的微处理器监控器具有去抖动的手动复位输入,有助于忽略这种振铃。

2023-06-26 15:34:47 534

534

的供应商,拥有遍布世界各地的60,000客户,涵盖了全部类型的电子设备制造商。作为领先业界40多年的高性能模拟集成电路(IC)制造商,ADI的产品广泛用于模拟信号和数字

2023-06-21 17:47:18 217

217

的供应商,拥有遍布世界各地的60,000客户,涵盖了全部类型的电子设备制造商。作为领先业界40多年的高性能模拟集成电路(IC)制造商,ADI的产品广泛用于模拟信号和数字

2023-06-21 17:47:10 217

217

M261在使用内部时钟的条件下,最低运行时钟是多少MHZ?

24MHz吗?

2023-06-20 07:34:49

的供应商,拥有遍布世界各地的60,000客户,涵盖了全部类型的电子设备制造商。作为领先业界40多年的高性能模拟集成电路(IC)制造商,ADI的产品广泛用于模拟信号和数字信号处理领域。公司总部设在美国马萨诸塞州诺伍德市,设计和制造基地遍布全球。ADI公司被纳入标准普尔

2023-06-19 09:05:02 157

157

精度,无需牺牲直流精度来换取更高的采样速率。然而,为实现高交流性能,如信噪比(SNR),系统设计人员必须考虑采样时钟信号或控制ADC中采样保持(S&H)开关的转换启动信号上的抖动所带来的误差。随着目标信号和采样速率的增加,控制采样保持开关的信号抖动会成为主要误差源。

2023-06-15 16:30:12 381

381

本抖动简介介绍了各种抖动类型的定义,包括随机抖动类型:高斯、周期间、相邻周期;和确定性抖动类型:占空比失真、脉冲宽度失真、脉冲偏斜和数据相关(模式)抖动。应用笔记还讨论了各种抖动元件与系统误码率(BER)之间的关系。

2023-06-10 14:44:39 2077

2077

定时抖动、边沿速度、像差、光色散和衰减都会影响 SDH/SONET 接收器的高速时钟恢复性能。这些效应通过减少接收的不归零(NRZ)传输信号的“眼开度”来减少可用于无差错数据恢复的时间。光接收器包含

2023-06-10 14:30:53 605

605

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 1121

1121

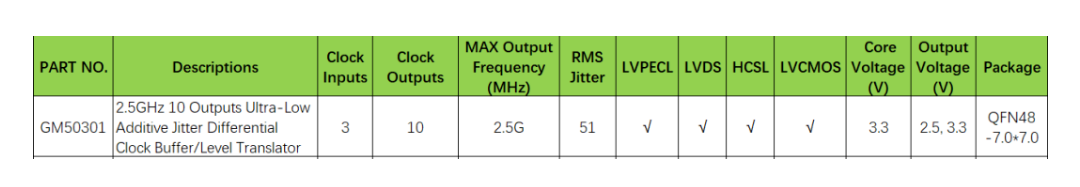

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

2023-06-08 15:30:21 526

526

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

2023-06-08 15:29:55 805

805

不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter Wander反映的主要是时钟源随着时间、温度等的缓慢变化,影响的是时钟或定时信号的绝对

2023-06-02 17:53:10

首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。

2023-06-02 09:09:06 1024

1024

发射端涉及到抖动的来源有:Thermal Noise(随机抖动), Duty Cycle Distortion(占空比失真), Power Supply Noise(随机抖动和周期性抖动), On chip coupling(周期性抖动)。

2023-05-31 16:43:28 947

947

) 以及其他通常要求时域抖动规范(如周期)的应用生成时钟- 周期和周期抖动。 然而,对于串行解串器 (SerDes)、千兆以太网 (GbE)、10 GbE、同步光网络/同步数字体系 (SONET/SDH) 和光纤通道等高速接口,情况就不同了。有严格的频域抖动要求。 为了正常运行,这些高速接口依赖于低频

2023-05-26 22:15:02 1385

1385 PD/QC快充电源ic U6648具有±5%的随机频率抖动功能,开关频率抖动分散了谐波扰动能量,获得良好的EMI特性。

2023-05-08 10:53:03 259

259 的 DDR 控制器中启用 DDR 时钟的最低要求是什么。在 DDR_SDRAM_CFG 中启用 MEM_EN 时,在 DDR 时钟启动之前是否必须有一组最小的 DDR 设置,即使其余配置还不

2023-05-06 08:20:49

NIST将抖动定义为“数字信号的重要时刻从其理想位置的短期相位变化”。我们将抖动想象为波的位置变化,形成从它应该在的位置上升或下降沿(“它应该在哪里”的很多意思是导致设计人员可能必须考虑的不同类型的抖动 - 稍后会详细介绍)。

2023-05-05 10:33:24 545

545

的供应商,拥有遍布世界各地的60,000客户,涵盖了全部类型的电子设备制造商。作为领先业界40多年的高性能模拟集成电路(IC)制造商,ADI的产品广泛用于模拟信号和数字

2023-04-19 09:52:53 222

222

随着数据速率的增加,链路抖动允许量变得越来越严格。硬件工程师将主要精力放在如何使他们的整个线路卡能够支持最大吞吐量,而为基准时钟产生的随机抖动分配尽可能小的允许量。针对基准时钟,对于一条25GbE

2023-04-17 10:37:30 357

357

展频IC在4M时钟上的应用

2023-04-14 10:12:27 0

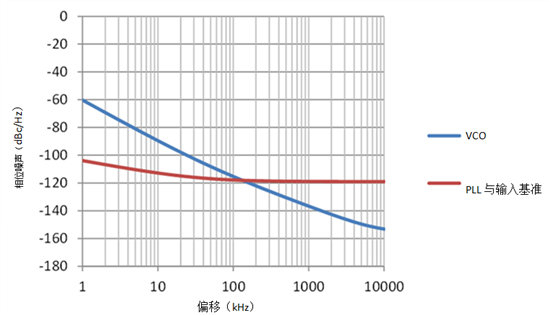

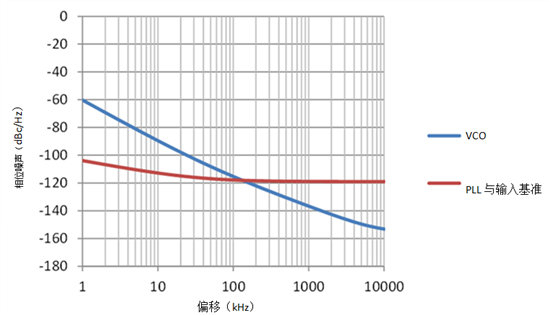

0 作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要做的仍是寻找最优环路带宽。

2023-04-12 10:32:17 1946

1946

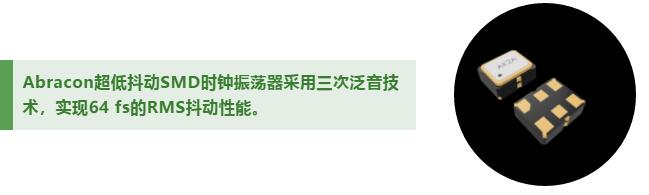

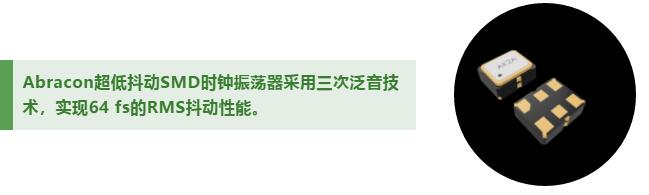

Abracon最新推出的超低抖动时钟系列AK2A和AK3A,旨在为数据中心、100G/400G/800G以太网和光模块等高速应用提供稳定准确的时钟信号

2023-04-11 17:00:08 492

492

本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 810

810

今天我们将讨论时钟如何影响精密 ADC,涉及时钟抖动、时钟互调和时钟的最佳 PCB 布局实践。

2023-04-11 09:13:22 644

644 600当我们尝试设置 6.5 MHz 像素时钟时,显示无法正常工作。请分享有关上述设置的信息,1. NXP IMX8MP支持的最低像素时钟频率2. 使用此配置,为双屏显示工作配置的最佳像素频率是多少。

2023-04-11 06:26:42

在时钟芯片方向,有容微电子基于优秀的时钟芯片团队、卓越的时钟芯片技术,着眼于满足不同客户、不同应用的差异化需求,致力于向广大客户提供具有完全自主知识产权的国产化时钟解决方案。

2023-04-07 15:08:00 930

930

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1633

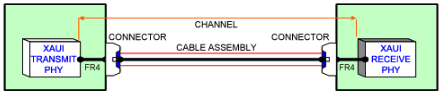

1633 高速串行链路的表征取决于SI工程师发现、理解和解决严重抖动问题的能力。在本讨论中,我们假设 PHY(物理层)或 SerDes(串行器-解串器)设备的时钟和数据恢复 (CDR) 模块符合适用于该设备

2023-04-03 11:27:21 995

995

BOARD EVAL FOR AD9525

2023-03-29 22:50:33

AD8655/AD8656是精密CMOS放大器,具有业界最低的噪声。二者采用ADI的DigiTrim®技术,以获得高dc精度

2023-03-28 18:29:15

CDCLVC1102 低抖动 1:2 LVCMOS 扇出时钟缓冲器

2023-03-28 18:26:07

CDCM61002 1:2 超低抖动晶体时钟发生器

2023-03-28 18:26:06

抖动和相位噪声是晶振的非常重要指标,本文主要从抖动和相位噪声定义及原理出发,阐述其在不同场景下对数字系统、高速串行接口、数据转换器和射频系统的影响。

2023-03-26 09:09:11 693

693

德赢Vwin官网

App

德赢Vwin官网

App

评论