前言

在2018年度的国际固态电路会议(ISSCC)上,有几项在图像传感器技术方面的新进展亮相,超越了以前着重在“选美”的图像撷取,添加了更多情境信息;这些新进展包括了事件导向(event-driven)传感器、能解决运动中物体图像扭曲问题的全局快门(global shutters)新方法,以及飞行时间(ToF)图像传感器。

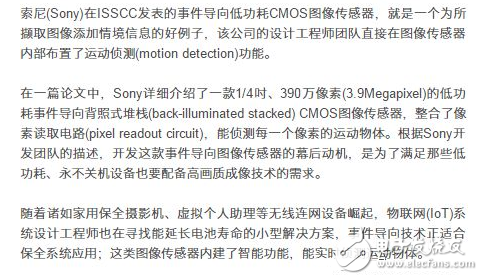

具备动作侦测功能的CMOS图像传感器

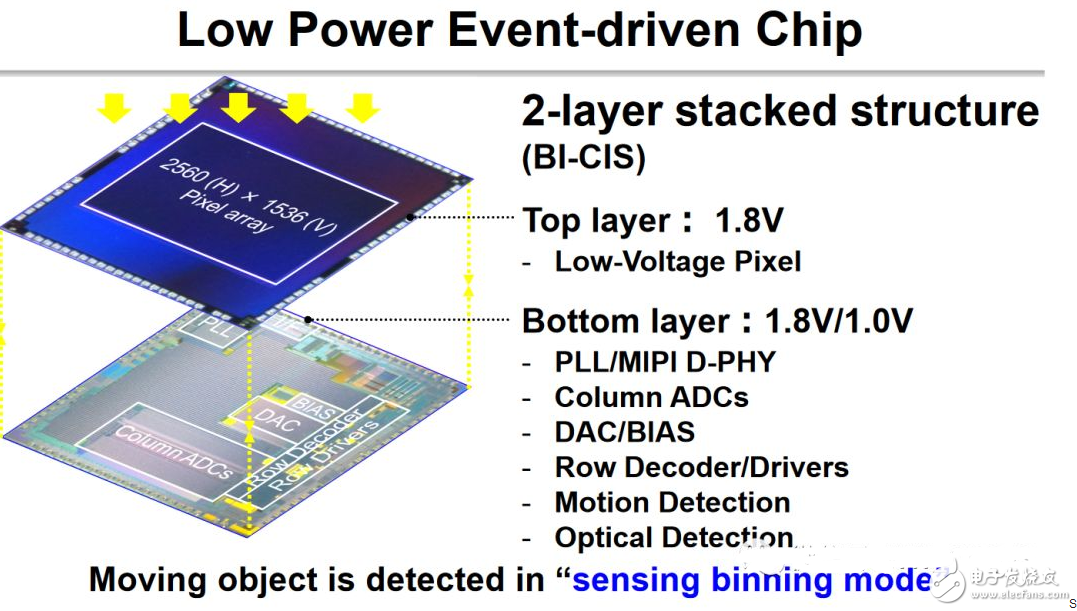

Sony的事件导向传感器具备像素数组、列驱动器(row drivers)、列译码器(row decoders)、单斜率产生器(single-slope generation)、动作/光侦测功能区块、图像信号处理器、讯框内存SRAM、MIPI链接端口,以及连结至传感器控制区块的CPU (来源:Sony)

Sony事件导向传感器功能区块

ToF传感器技术进展

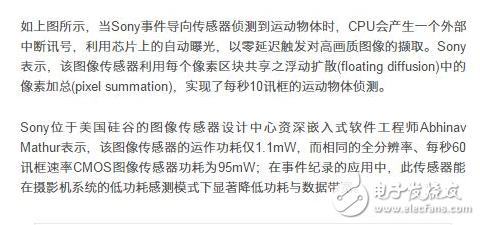

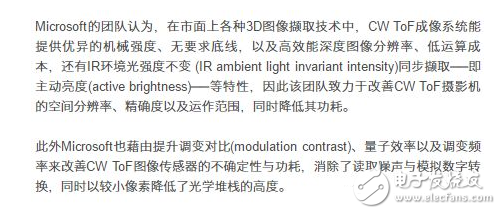

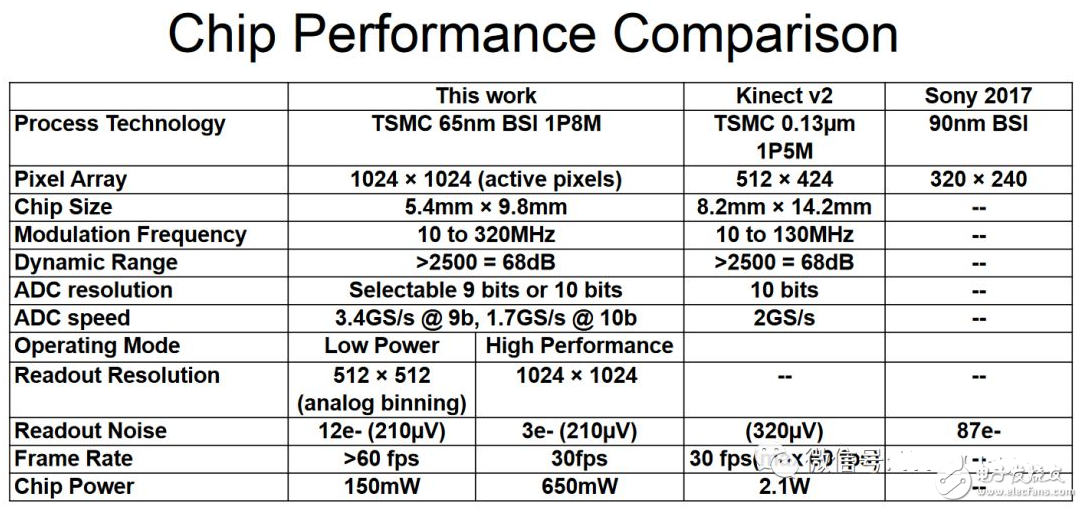

3D深度摄影机正夯,相关技术的竞争焦点在于更高分辨率、更低功耗以及更小体积;微软(Microsoft)在ISSCC简报了应用于Kinect 2动作感测设备的ToF传感器进展,该传感器采用的是经过改善的连续波(Continuous-Wave,CW)式ToF技术,号称将最新的ToF传感器推向了百万像素等级。

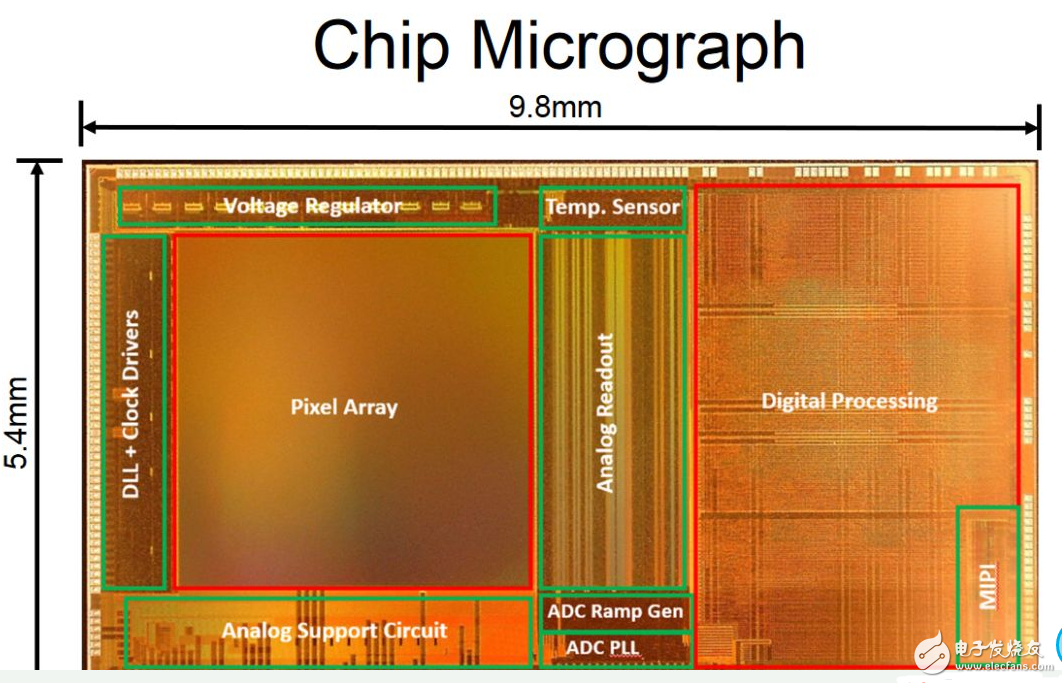

Microsoft的最新ToF传感器

Microsoft的ToF传感器规格

小型像素(3.5 x 3.5μm)对新一代ToF传感器在智能手机应用的竞争上非常重要,Microsoft号称其方案具备商用全局快门RGB传感器竞争力,以及适用手持式设备的小型光学堆栈;该公司在ISSCC论文中介绍的1024x1024像素ToF全局快门图像传感器,能在200MHz下达到87%的调变对比,采用台积电(TSMC)的65奈米1P8M背照式CMOS技术。

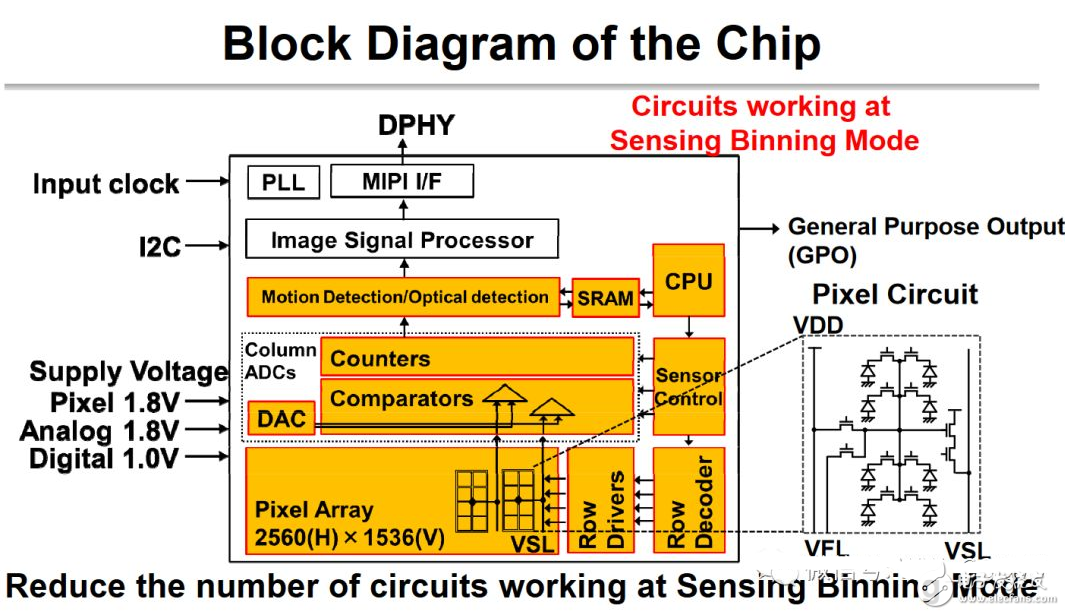

像素内噪声消除

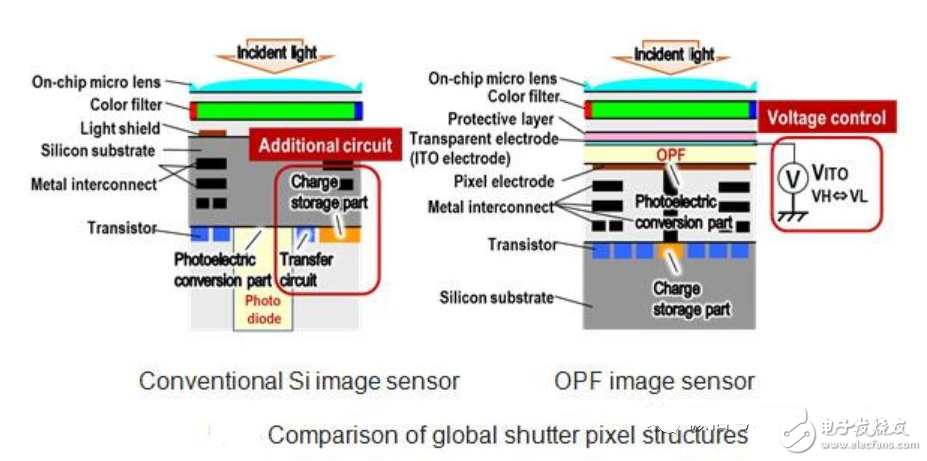

松下(Panasonic)在ISSCC展示其有机光导薄膜(organic photoconductive film,OPF) CMOS图像传感器技术最新进展──将OPF CMOS图像传感器中的光电转换功能与电路分离;藉由这种独特架构,该公司团队将新开发的高速噪声消除技术以及高饱和度技术整合至电路,同时利用传感器的独特敏感度控制功能来改变施加到OPF的电压,因此实现全局快门功能。

OPF CMOS图像传感器与传统全局快门传感器的架构比较;Panasonic声称其最新传感器是业界首款提供8K分辨率、60fps讯框速率、450k电子饱和度,并具备全局快门功能 (来源:Panasonic)

在过去,广播电视与保全应用的高分辨率、高保真度摄影机,如8K超高分辨率电视系统与采用堆栈传感器方案的8K摄影机的共同缺陷,是采用滚动快门(rolling-shutter)而非全局快门。在全局模式下,快门运作能同步撷取所有像素的图像;而滚动快门模式的有机CMOS图像传感器,则是以逐行(row by row)方式曝光与运作。

Panasonic表示,滚动快门会导致失真问题,特别是在高速成像以及多视角图像合成应用时

Panasonic新开发的传感器号称能实时撷取不失真的运动物体图像,该公司认为这对多视角与高速、高分辨率摄影机特别有益,例如机器视觉与智能交通监控系统的应用;而因为光电转换与电路能分开设计,利用像素内增益开关(in-pixel gain-switching)技术能达到高饱和度特性,电压控制敏感度调变技术则是藉由改变施加至OPF的电压来调整敏感度。

Panasonic新开发的CMOS图像传感器能撷取8K分辨率图像,甚至在高对比度度的场景中,同时具备全局快门功能,可用全像素撷取同步图像 (来源:EE Times)

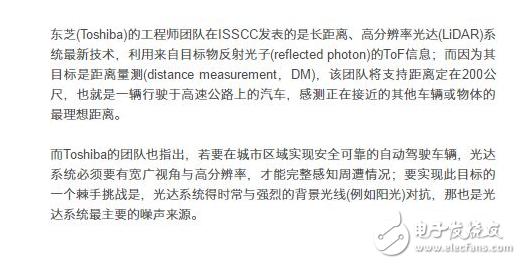

支持200公尺距离的成像光达

车用光达系统的侦测距离要求以及Toshiba的解决方案规格

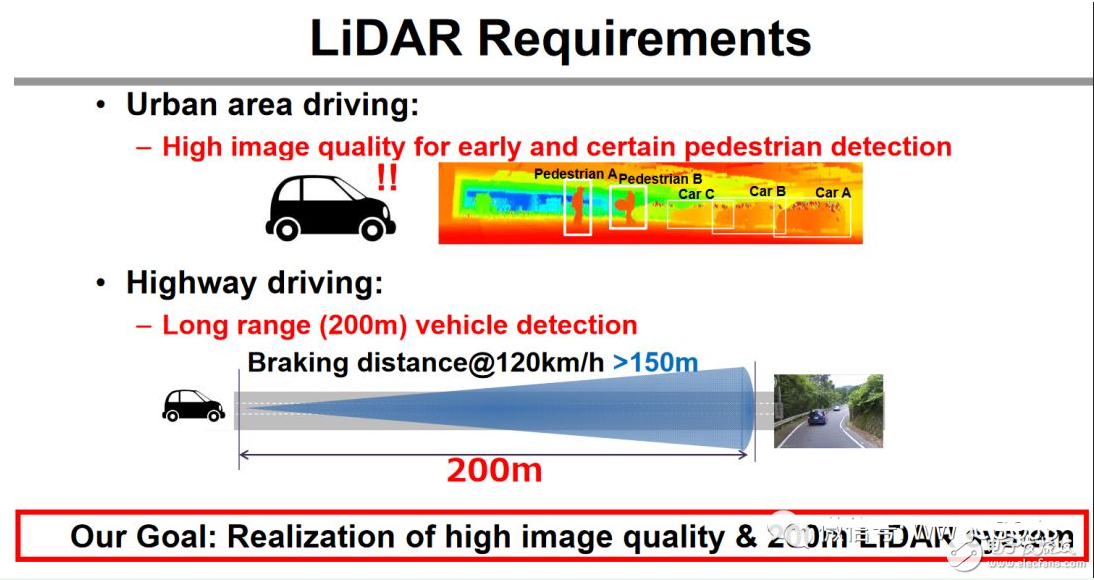

Toshiba介绍了一种结合时间至数字值转换器(Time-to-Digital Converter,TDC)与vwin 数字转换器(ADC)的光达SoC,配备了一种命名为智能累加技术(Smart Accumulation Technique,SAT)的功能,号称能让光达系统达到200公尺的视距以及自动驾驶车辆需要的高分辨率图像。

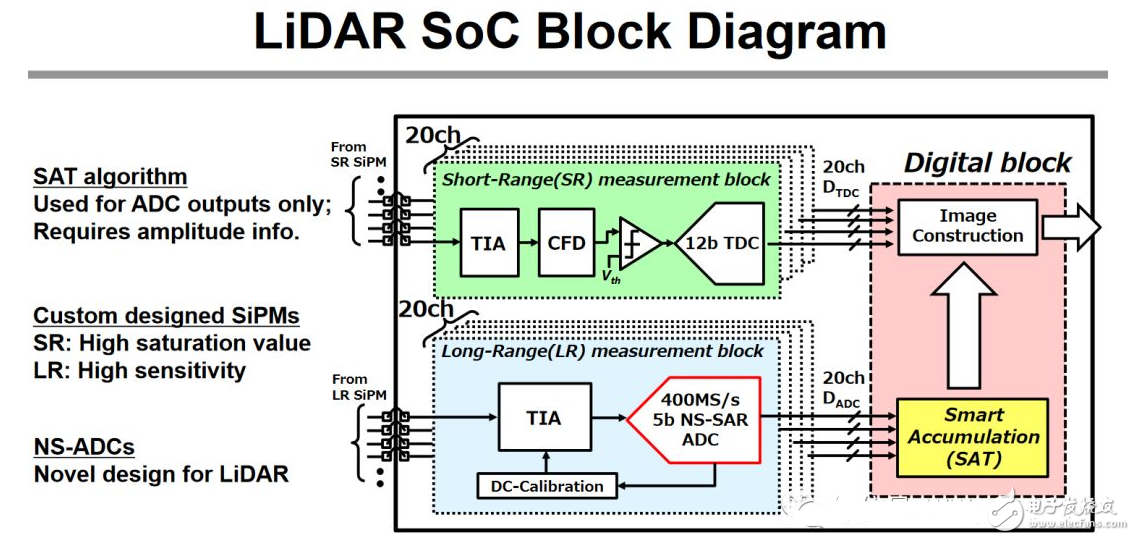

根据Toshiba的说法,SAT能利用来自ADC的强度与背景光信息,识别并累计仅从目标物反射的数据,因此与传统的累加技术相较,其分辨率能达到四倍。该TDC/ADC组合架构放宽了ADC采样率需求,以支持短距离DM精确度;此外该概念验证支持200公尺距离的光达系统,DM距离是传统设计的两倍,可实现240x96像素分辨率与0.125%的DM精确度。

Toshiba光达方案与传统设计的性能比较

像素平行接合技术

不只Panasonic,Sony也注意到滚动快门图像传感器撷取运动物体图像失真的问题,指出像素内模拟内存(in-pixel analog memory)与像素平行(pixel-parallel) ADC虽是潜在解决方案,但这些技术都无法支持百万像素分辨率,因为它们都没有解决在一个像素中读写ADC数字讯号的时序限制(timing constraint)问题。

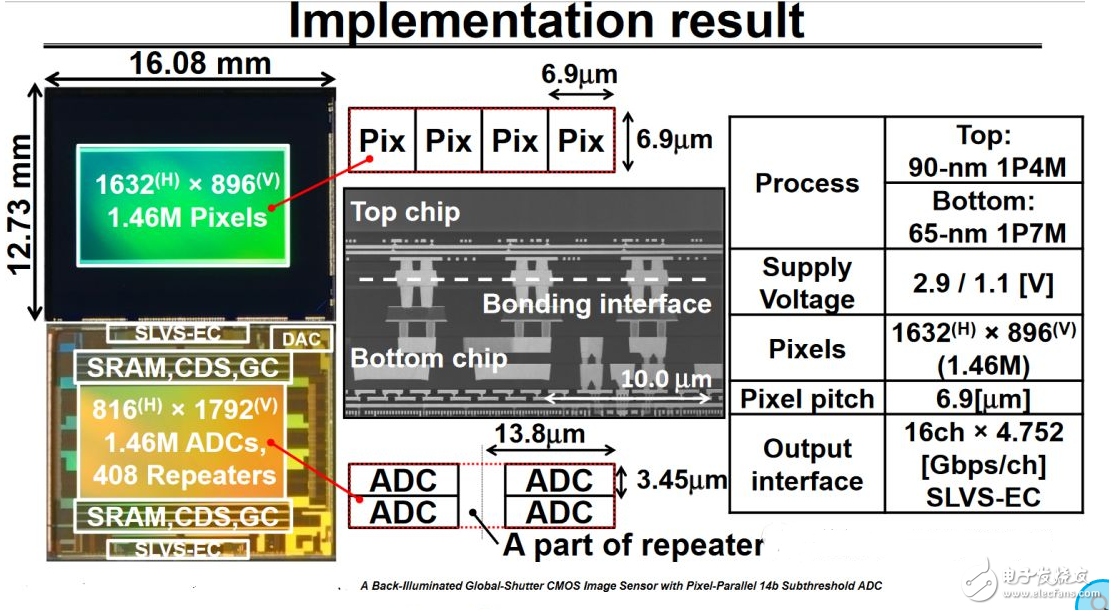

Sony在ISSCC论文中提出的方案,是利用具备每像素单一ADC的堆栈图像传感器,在CMOS传感器实现全局快门

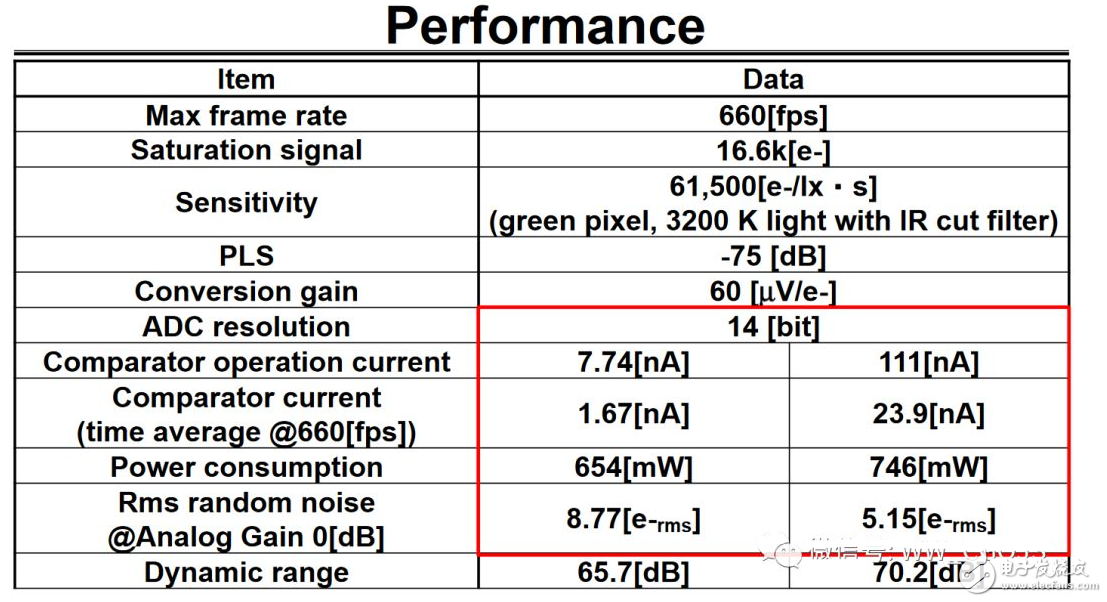

Sony的堆栈式背照CMOS图像传感器,配备146万像素14位ADC,采用像素级接合技术(pixel-level bonding technology)。该公司表示,具备正向回馈电路的次临界值比较器(subthreshold comparator)有助于降低比较器运作电流与电路区域最小化,能降低功耗。